Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:16.

- Última modificació 2025-01-23 14:38.

Aquest és un tutorial sobre com construir un cronòmetre d’un minut mitjançant VHDL i una placa Basys 3. Aquest dispositiu és ideal per a jocs on cada jugador té un màxim d’un minut per fer el seu moviment. El cronòmetre mostra amb precisió segons i mil·lisegons a la pantalla de set segments, a partir de 0 segons i 0 mil·lisegons, fins a 60 segons i 0 mil·lisegons. També s’utilitzen dos botons: el botó central, utilitzat per iniciar, aturar i continuar el temporitzador, i el botó dret, que s’utilitza per reiniciar el temporitzador. Quan es compara el dispositiu un al costat de l’altre amb el cronòmetre incorporat d’un telèfon intel·ligent, es nota la precisió del rellotge.

Pas 1: Obteniu maquinari / programari

1. Basys 3 Artix-7 FPGA Trainer Board de Digilent amb cable micro-USB a USB

2. Vivado 2016.2 Design Suite de Xilinx

Pas 2: diagrama de blocs

Aquest circuit es construeix de manera conductual i utilitza components Xilinx integrats, però també es pot descriure estructuralment, tal com es mostra al diagrama estructural general anterior. Pel diagrama es pot veure que el circuit està conduït per dos divisors de freqüència. Un dels divisors de freqüència funciona a 1 centisegon i condueix el comptador de càtodes que s’utilitza com a números que es mostren a la pantalla de set segments. El segon divisor de freqüència funciona a 240Hz i s’utilitza per conduir el comptador d’ànodes que gira a través dels ànodes de manera que tots els números es mostrin correctament a la pantalla de set segments. El codificador pren la lògica del càtode del comptador de càtodes i la lògica de l’ànode del comptador d’ànodes i la codifica al càtode i ànode de la sortida que executen la pantalla de set segments. La funció d’aquest codificador és que la sortida del càtode canviï cada vegada que canviï la sortida de l’ànode. La sortida del càtode no es pot executar independentment del comptador perquè els ànodes han de girar a través dels 4 dígits separats.

Pas 3: Mòdul de projecte

En primer lloc, es fa un bloc de procés per a CEN de manera que quan es detecta una pulsació de botó, l'ACTIVACIÓ canviarà. Això serveix com a parada / arrencada del comptador de càtodes.

Al següent bloc de procés, els senyals de rellotge de centisegons i 240Hz es configuren de manera que els seus comptadors respectius augmentin 1 cada vegada que el rellotge intern de 100 MHz arriba a una vora ascendent. Un cop el comptador de centisegons arribi a 500.000, es tornaria a restablir a 0. Mentrestant, el comptador de 240Hz es restabliria un cop el recompte arribés als 4.1667.

Per a la secció del càtode del codi, si ENABLE és '0', el recompte del càtode es posarà en pausa. Si es prem el botó de reinici durant aquest temps, tots els recomptes es restabliran a "0000". Mentrestant, si ENABLE és '1', el recompte de càtodes continuarà fins que el recompte de càtodes arribi a 60.00, en el qual activarà el senyal d'aturada com a '1'. El senyal d'aturada es dirigeix cap al bloc de procés CEN i fa que ENABLE sigui '0' mentre el senyal d'aturada sigui '1' i no canviarà fins que no es prem el botó de reinici.

Finalment, la visualització de set segments es configura tenint els 4 ànodes connectats correctament amb cadascun dels seus 8 càtodes per mostrar els seus respectius dígits 0-9 simultàniament.

Pas 4: restriccions

Aquest fitxer de restriccions connecta les entrades i sortides especificades de VHDL a les parts físiques necessàries de la placa Basys. Per a aquest projecte, els components inclouen els quatre ànodes i cadascun dels seus vuit càtodes per a la pantalla de set segments, el rellotge intern de 100 MHz, el botó central i el botó dret.

Pas 5: prova

Un cop hàgiu completat el codi, ara podeu programar l'FPGA mitjançant el cable USB. La pantalla de set segments ha de mostrar 0,00. Proveu si els botons funcionen prement el botó central per iniciar el temporitzador fins que arribi a les 60.00 i s'aturi; en qualsevol moment, podeu tornar a prémer el botó central per aturar-lo. Un cop estigui en pausa, podeu prémer el botó dret per restablir el temporitzador a 0,00. Si tot funciona correctament, enhorabona, acabeu de crear un temporitzador d’un minut.

Recomanat:

Cronòmetre Arduino Leonardo: 3 passos

Cronòmetre Arduino Leonardo: Crèdit: https://www.instructables.com/id/Arduino-Stopwatch … Aquest disseny del cronòmetre es va originar a l’enllaç de dalt, que és un cronòmetre que compta des de l’1, mentre que aquest compte enrere a partir dels 60 segons . La majoria del codi que he utilitzat segueix l'original

Cronòmetre De Cocina. Arbre de la vida: 4 passos

Cronòmetre De Cocina. Tree of Life: El cron ó metro de cuina és una eina que li permet a l’estudiant realitzar diverses tareas sense perdre l’atenció ó n dels temps de la cuina. Funciona com un cron ó metro midiendo intervalos de 10 min, cada lapso de tiempo s

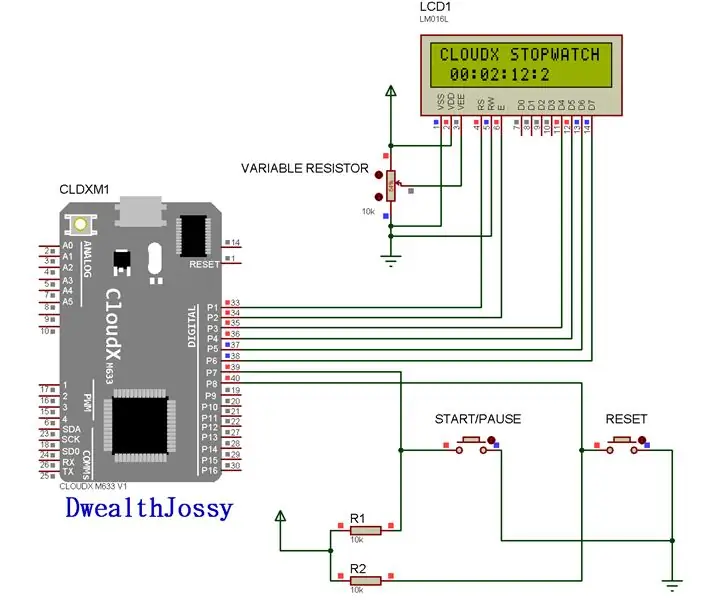

Cronòmetre digital simple CloudX M633: 4 passos

Cronòmetre digital simple CloudX M633: en aquest projecte, farem una versió d’un rellotge digital que pugui guardar un registre d’hores, minuts i segons, igual que un cronòmetre al vostre telèfon mòbil. Utilitzarem una pantalla LCD per mostrar l'hora

Cronòmetre bàsic amb VHDL i Basys3 Board: 9 passos

Cronòmetre bàsic amb la placa VHDL i Basys3: us donem la benvinguda a la informació sobre com construir un cronòmetre mitjançant la placa bàsica VHDL i Basys 3. Estem encantats de compartir el vostre projecte amb vosaltres! Aquest va ser un projecte final del curs CPE 133 (Disseny digital) a Cal Poly, SLO a la tardor del 2016. El projecte que vam construir

Cronòmetre VHDL: 8 passos (amb imatges)

Cronòmetre VHDL: es tracta d’un tutorial sobre com fer un cronòmetre amb VHDL i una placa de circuit FPGA, com una placa Basys3 Atrix-7. El cronòmetre pot comptar de 00.00 segons a 99.99 segons. Utilitza dos botons, un per al botó d'inici / atura i un altre per al botó