Taula de continguts:

- Pas 1: conceptes bàsics de les pantalles de cristall líquid

- Pas 2: diagrama de blocs bàsic de disseny de GreenPAK

- Pas 3: dissenyar el consum actual

- Pas 4: esquema del dispositiu GreenPAK

- Pas 5: interfície I²C

- Pas 6: controlador del segment de sortida

- Pas 7: control de la font del rellotge de l’oscil·lador intern i del pla posterior

- Pas 8: sortida del rellotge del pla posterior o control del pin de sortida del segment 15

- Pas 9: prototip del sistema LCD

- Pas 10: ordres I²C per al control LCD

- Pas 11: ordres I²C per a la prova LCD

- Pas 12: Resultats de les proves

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:10.

- Última modificació 2025-01-23 14:37.

Les pantalles de cristall líquid (LCD) s’utilitzen àmpliament per a aplicacions comercials i industrials a causa de les seves bones propietats visuals, el seu baix cost i el seu baix consum d’energia. Aquestes propietats fan que la pantalla LCD sigui la solució estàndard per a dispositius amb bateria, com ara instruments portàtils, calculadores, rellotges, ràdios, etc.

Tot i això, per controlar adequadament el que mostra la pantalla LCD, el controlador electrònic de la pantalla LCD ha de generar formes d’ona de voltatge adequades als pins LCD. Les formes d'ona haurien de ser de corrent altern (corrent altern) perquè les tensions de corrent continu (corrent continu) danyaran permanentment el dispositiu. El controlador adequat proporcionaria aquests senyals a LCD amb un consum mínim d’energia.

Existeixen dos tipus de pantalles LCD, les estàtiques, amb només un pla posterior i un pin per al control de segments individuals i, el multiplexat, amb diversos pla posterior i múltiples segments connectats per a cada pin.

En aquest manual es presentarà el disseny d'un controlador LCD estàtic amb el dispositiu SLP46537V GreenPAK ™. El controlador LCD dissenyat conduiria fins a 15 segments de LCD, utilitzant alguns microamperis de corrent de la font d'alimentació i oferiria una interfície I²C per al control.

A les seccions següents es mostraran:

● informació bàsica sobre els LCD;

● el disseny del controlador LCD SLP46537V GreenPAK en detall;

● com conduir un LCD estàtic de quatre dígits de set segments amb dos dispositius GreenPAK.

A continuació es descriuen els passos necessaris per comprendre com s'ha programat la solució per crear el controlador LCD estàtic amb interfície I²C. Tot i això, si només voleu obtenir el resultat de la programació, descarregueu-vos el programari GreenPAK per veure el fitxer de disseny GreenPAK ja completat. Connecteu el kit de desenvolupament GreenPAK a l'ordinador i premeu el programa per crear el controlador LCD estàtic amb interfície I²C.

Pas 1: conceptes bàsics de les pantalles de cristall líquid

Les pantalles de cristall líquid (LCD) són una tecnologia que no emet llum, només controla com passa una font de llum externa. Aquesta font de llum externa podria ser la llum ambiental disponible, en el tipus de pantalla reflectant, o la llum d'un llum o llum de fons, en tipus de pantalla transmissiva. Les pantalles LCD es construeixen amb dues plaques de vidre (superior i inferior), una fina capa de cristall líquid (LC) entre elles i dos polaritzadors de llum (Nota d’aplicació AN-001 - Fonaments bàsics de la tecnologia LCD, Hitachi, Nota d’aplicació AN-005 - Pantalla Modes, Hitachi). El polaritzador és un filtre de llum per al camp electromagnètic de llum. Només els components lleugers en la direcció correcta del camp electromagnètic passen pel polaritzador, mentre que la resta de components estan bloquejats.

El cristall líquid és un material orgànic que gira el camp electromagnètic de la llum 90 graus o més. No obstant això, quan s’aplica un camp elèctric a la LC ja no gira la llum. Amb l’addició d’elèctrodes transparents al vidre de visualització superior i inferior, es pot controlar quan passa la llum i quan no, amb una font externa del camp elèctric. La figura 1 (vegeu la nota d'aplicació AN-001 - Conceptes bàsics de la tecnologia LCD, Hitachi) anterior il·lustra aquest control d'operació. A la figura 1, la pantalla és fosca quan no hi ha un camp elèctric. Això es deu al fet que tots dos polaritzadors filtren la llum en la mateixa direcció. Si els polaritzadors són ortogonals, la pantalla quedarà fosca quan hi hagi el camp elèctric. Aquesta és la situació més freqüent per a les pantalles reflectants.

El camp elèctric mínim, o tensió, per controlar la pantalla LCD s’anomena llindar ON. El LC només es veu afectat per la tensió i amb prou feines hi ha corrent en el material LC. Els elèctrodes de la pantalla LCD formen una petita capacitat i aquesta és l’única càrrega per a un conductor. Aquesta és la raó per la qual un LCD és un dispositiu de baixa potència per mostrar informació visual.

Tot i això, és important tenir en compte que la pantalla LCD no pot funcionar amb una font de tensió de corrent continu (CC) durant massa temps. L’aplicació d’una tensió de corrent continu provocarà reaccions químiques en el material LC i el perjudicarà permanentment (Nota d’aplicació AN-001 - Fonaments bàsics de la tecnologia LCD, Hitachi). La solució és aplicar una tensió alternativa (CA) als elèctrodes LCD.

A les pantalles LCD estàtiques, s’inclou un elèctrode de la placa posterior en un vidre i els segments individuals, o píxels, es col·loquen a l’altre vidre. Aquest és un dels tipus de LCD més senzills i amb la millor relació de contrast. No obstant això, aquest tipus de pantalla sol requerir massa pins per controlar cada segment individual.

En general, un controlador de controlador genera un senyal de rellotge d'ona quadrada per al pla posterior i un senyal de rellotge per als segments del pla frontal junts. Quan el rellotge del pla posterior està en fase amb el rellotge del segment, la tensió mitjana-arrel (RMS) entre els dos plans és nul·la i el segment és transparent. En cas contrari, si el voltatge RMS és superior al llindar de l'LCD ON, el segment es fa fosc. Les formes d'ona per al pla posterior, el segment activat i desactivat es mostren a la figura 2. Com es pot veure a la figura, el segment ON està desfasat en relació amb el senyal del pla posterior. El segment off està en fase en relació amb el senyal del pla posterior. El voltatge aplicat podria estar entre 3 i 5 volts per a pantalles de baix cost i poca potència.

El senyal de rellotge de la placa posterior i els segments de la pantalla LCD solen estar entre 30 i 100 Hz, la freqüència mínima per evitar un efecte de parpelleig visual a la pantalla LCD. S'eviten freqüències més altes per reduir el consum d'energia del sistema general. El sistema compost per LCD i controladors consumiria poc corrent, en l’ordre dels microamperis. Això els fa perfectament adequats per a aplicacions de fonts d’alimentació i bateria de baixa potència.

A les seccions següents, es presenta detalladament el disseny d’un controlador estàtic LCD amb dispositiu GreenPAK que pot generar el senyal de rellotge del pla posterior i el senyal de rellotge de segment individual per a un LCD comercial.

Pas 2: diagrama de blocs bàsic de disseny de GreenPAK

Un diagrama de blocs que il·lustra el disseny GreenPAK es mostra a la figura 3. Els blocs bàsics del disseny són la interfície I²C, el controlador del segment de sortida, l’oscil·lador intern i el selector de font de rellotge del pla posterior.

El bloc d'interfície I²C controla la sortida de cada segment individual i la font del rellotge del pla posterior de la pantalla LCD. El bloc d'interfície I²C és l'única entrada del sistema per al control de sortida de segments.

Quan s'estableix la línia de control del segment intern (nivell alt), el segment LCD corresponent és opac fosc. Quan es restableix la línia de control del segment intern (nivell baix), el segment LCD corresponent és transparent.

Cada línia de control del segment intern està connectada a un controlador de sortida. El bloc del controlador del segment de sortida generarà un senyal de rellotge en fase amb relació amb el rellotge del pla posterior per a segments transparents. Per als segments foscos, aquest senyal està desfasat en relació amb el rellotge del pla posterior.

La font del rellotge del pla posterior també es selecciona amb la interfície I²C. Quan se selecciona la font interna del rellotge del pla posterior, l'oscil·lador intern s'encén. L’oscil·lador intern generarà una freqüència de rellotge de 48Hz. Aquest senyal l’utilitzarà el bloc del controlador del segment de sortida i s’adreça al pin de sortida del rellotge del pla posterior (pin 20 de GreenPAK).

Quan se selecciona la font de rellotge del pla posterior posterior, l’oscil·lador intern s’apaga. La referència del controlador del segment de sortida és l’entrada de rellotge del pla posterior posterior (pin 2 de GreenPAK). En aquest cas, el pin de sortida del rellotge del pla posterior es podria utilitzar com a línia de control de segment addicional, el segment OUT15.

Es pot utilitzar més d'un dispositiu GreenPAK a la mateixa línia I²C. Per fer-ho, cada dispositiu ha de ser programat amb una adreça I²C diferent. D'aquesta manera és possible ampliar el nombre de segments LCD impulsats. Un dispositiu està configurat per generar la font del rellotge de la placa posterior, que condueix 14 segments, i els altres estan configurats per utilitzar una font de rellotge externa. Cada dispositiu addicional podria conduir més 15 segments d'aquesta manera. És possible connectar fins a 16 dispositius a la mateixa línia I²C i llavors és possible controlar fins a 239 segments d'una pantalla LCD.

En aquesta instrucció, s’utilitza aquesta idea per controlar 29 segments d’una pantalla LCD amb 2 dispositius GreenPAK. La funcionalitat de fixació del dispositiu es resumeix a la taula 1.

Pas 3: dissenyar el consum actual

Una preocupació important en aquest disseny és el consum actual, que hauria de ser el més baix possible. El corrent de repòs estimat del dispositiu GreenPAK és de 0,75 µA per a l'operació de subministrament de 3,3 V i 1,12 µA per a l'operació de subministrament de 5 V. El consum de corrent de l'oscil·lador intern és de 7,6 µA i 8,68 µA per al funcionament de la font d'alimentació de 3,3 V i 5 V respectivament. No s’espera que augmenti significativament el consum actual per pèrdues de commutació, perquè aquest disseny funciona a una freqüència de rellotge baixa. El corrent màxim estimat consumit per a aquest disseny és inferior a 15 µA quan l’oscil·lador intern està encès i a 10 µA quan l’oscil·lador intern està apagat. El corrent mesurat consumit en ambdues situacions es mostra a la secció Resultats de la prova.

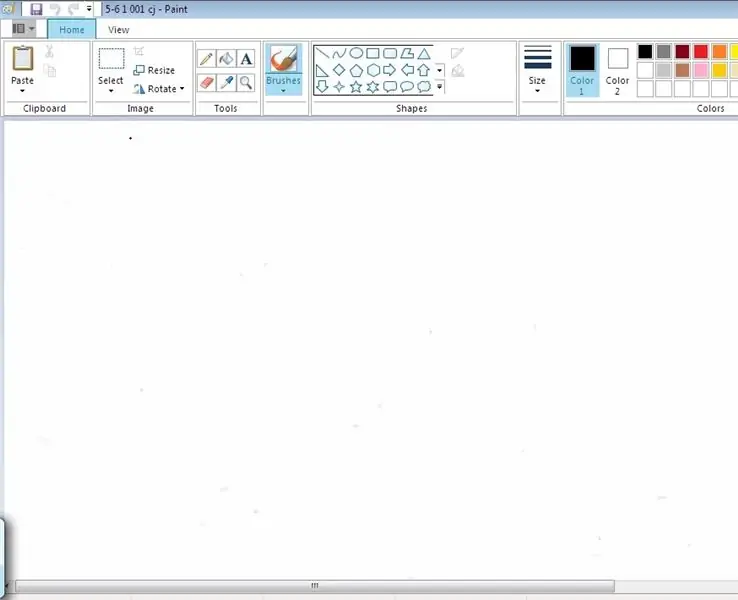

Pas 4: esquema del dispositiu GreenPAK

El projecte dissenyat amb el programari GreenPAK es mostra a la figura 4. Aquest esquema es descriurà utilitzant els diagrames de blocs bàsics com a referència.

Pas 5: interfície I²C

El bloc d'interfície I²C s'utilitza com a bloc de control principal del control de funcionament del dispositiu. A la figura 5 es mostra una vista propera a les connexions de blocs i a les propietats configurades.

Aquest bloc està connectat al PIN 8 i al PIN 9, que són pins SCL i SDA I²C respectivament. Dins del dispositiu, el bloc I²C ofereix 8 entrades virtuals. El valor inicial de cada entrada virtual es mostra a la finestra de propietats (vegeu la figura 5). Les entrades virtuals des de OUT0 fins OUT6 s’utilitzen com a línies de control de segments. Aquestes línies de control corresponen a la sortida de segment 1 a la sortida de segment 7 i estan connectades al controlador de sortida de segment. L'entrada virtual OUT7 s'utilitza com a control de línia de selecció de font de rellotge del pla posterior, amb el nom net BCKP_SOURCE. Aquesta xarxa serà utilitzada per altres blocs del disseny. El codi de control I²C es configura amb un valor diferent per a cada IC del projecte.

Hi ha 8 línies de control de segment intern més disponibles a la sortida de la màquina d’estats asíncrons (ASM), tal com es mostra a la figura 6 anterior. La línia de sortida del segment 8 (SEG_OUT_8 a la finestra de propietats) a través de la línia de sortida del segment 15 (SEG_OUT_15) està controlada per la sortida ASM a l'estat 0. No hi ha cap transició d'estat al bloc ASM, sempre està a l'estat 0. Les sortides d'ASM són connectat als controladors de sortida de segments.

Els controladors de sortida del segment generaran el senyal de sortida del dispositiu.

Pas 6: controlador del segment de sortida

El controlador del segment de sortida és essencialment una taula de cerca (LUT) configurada com a port lògic XOR. Per a cada segment de sortida, ha de ser un port XOR connectat a la línia de control de segments i al rellotge del pla posterior (BCKP_CLOCK). El port XOR és responsable de generar el segment de sortida de senyal en fase i fora de fase. Quan la línia de control del segment està a un nivell alt, la sortida del port XOR invertirà el senyal del rellotge del pla posterior i generarà un senyal fora de fase al pin del segment. La diferència de tensió entre el fons de pantalla LCD i el segment LCD, en aquest cas, configurarà el segment LCD com un segment fosc. Quan la línia de control del segment es troba a un nivell baix, la sortida del port XOR seguirà el senyal del rellotge del pla posterior i, a continuació, generarà un senyal en fase al pin del segment. Com que en aquest cas no s’aplica cap tensió entre la placa posterior i el segment LCD, el segment és transparent a la llum.

Pas 7: control de la font del rellotge de l’oscil·lador intern i del pla posterior

L'oscil·lador intern s'utilitza quan el senyal BCKP_CLOCK de la interfície I²C s'estableix a un nivell alt. A la Figura 7 anterior es mostra una vista propera del diagrama de control de la font del rellotge.

L'oscil·lador es configura com a freqüència RC de 25 kHz, amb el divisor de sortida més alt disponible a l'oscil·lador OUT0 (8/64). Tota la configuració es veu a la finestra de propietats que es mostra a la figura 7. D'aquesta manera, l'oscil·lador intern generarà una freqüència de rellotge de 48 Hz.

L'oscil·lador només està actiu quan el senyal BCKP_SOURCE es troba a un nivell alt junt amb el senyal POR. Aquest control es realitza connectant aquests dos senyals al port NAND del 4-L1 LUT. La sortida del NAND es connecta a l'entrada del pin de control de desconnexió de l'oscil·lador.

El senyal BCKP_SOURCE controla el MUX construït amb 3-L10 LUT. Quan el senyal BCKP_SOURCE està a un nivell baix, la font del rellotge del pla posterior prové del PIN2. Quan aquest senyal és a un nivell alt, la font del rellotge del pla posterior prové de l'oscil·lador intern.

Pas 8: sortida del rellotge del pla posterior o control del pin de sortida del segment 15

El pin 20 d’aquest disseny té una doble funció, que depèn de la font de rellotge seleccionada. El funcionament d’aquest pin es controla amb un LUT de 4 entrades, tal com es mostra a la figura 8. Amb un LUT de 4 bits, és possible associar el funcionament del port XOR amb un MUX de sortida. Quan el senyal BCKP_SOURCE es troba a un nivell alt, la sortida LUT seguirà el rellotge de l’oscil·lador intern. A continuació, el pin 20 funciona com a sortida de rellotge del pla posterior. Quan el senyal BCKP_SOURCE es troba a un nivell baix, la sortida LUT serà l'operació XOR entre SEG_OUT_15, des de la sortida ASM, i el senyal de rellotge del pla posterior. La configuració LUT de 4 bits per fer aquesta operació es mostra a la figura 8.

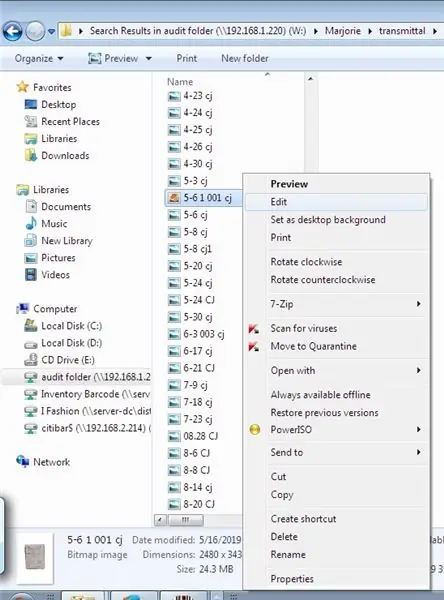

Pas 9: prototip del sistema LCD

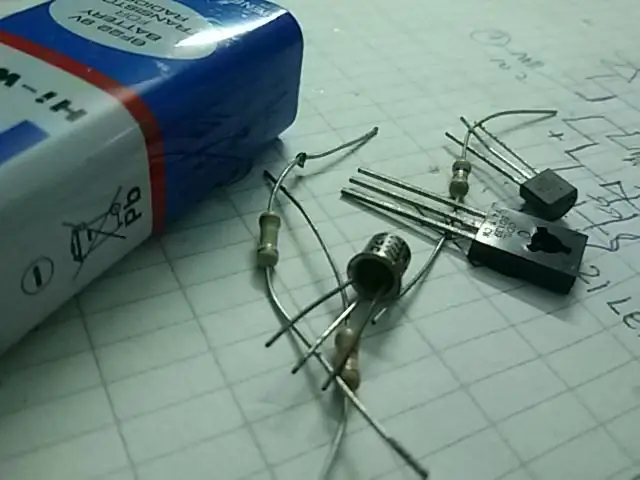

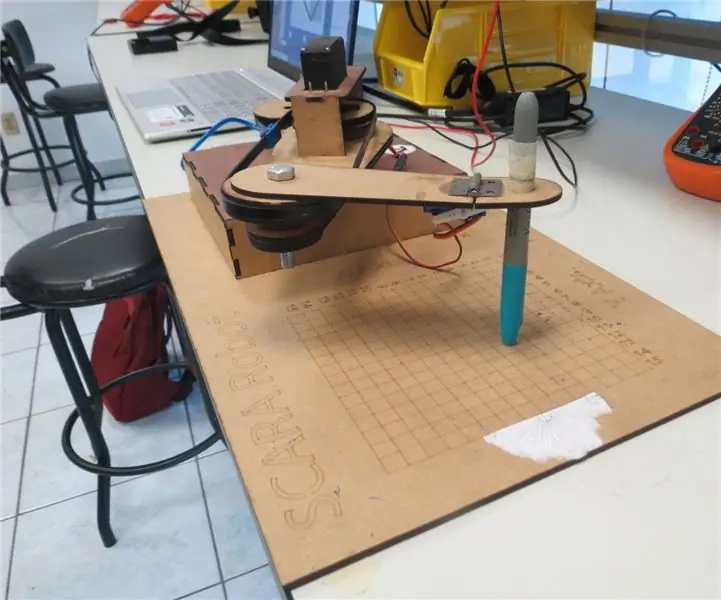

Per demostrar l'ús de la solució de disseny GreenPAK, es va muntar un prototip del sistema LCD en una taula de treball. Per al prototip, una pantalla estàtica de quatre dígits de set segments està impulsada per dos dispositius GreenPAK a la placa DIP. Un dispositiu (IC1) utilitza l'oscil·lador intern per conduir el pla posterior de LCD i l'altre dispositiu (IC2) utilitza aquest senyal com a referència d'entrada del pla posterior. Els dos circuits integrats es controlen a través de la interfície I²C mitjançant un microcontrolador (MCU) STM32F103C8T6 en una placa de desenvolupament mínima.

La figura 9 mostra l’esquema de les connexions entre els dos circuits integrats GreenPAK, la pantalla LCD i la placa MCU. A l’esquema, el dispositiu GreenPAK amb referència U1 (IC1) impulsa els dígits LCD un i dos (LCD a l’esquerra). El dispositiu GreenPAK amb referència U2 (IC2) impulsa els dígits LCD tres i quatre, més el segment COL (costat dret LCD). La font d'alimentació d'ambdós dispositius prové del regulador de la placa de desenvolupament de microcontroladors. S’afegeixen dos ponts extraïbles entre la font d’alimentació i els pins VDD de cada dispositiu GreenPAK per a la mesura de corrent amb un multímetre.

A la figura 10 es mostra una imatge del prototipus muntat.

Pas 10: ordres I²C per al control LCD

Els dos dispositius GreenPAK de la taula de programació es programen amb el mateix disseny, excepte pel valor de byte de control. El byte de control d'IC1 és 0 (adreça I²C 0x00), mentre que el byte de control I²C és 1 (adreça I²C 0x10). Les connexions entre els segments de visualització i els controladors de dispositiu es resumeixen a la taula anterior.

Les connexions es van seleccionar d’aquesta manera per crear un esquema més clar i simplificar el muntatge de les connexions de la placa.

El control de la sortida del segment es realitza mitjançant ordres d’escriptura I²C a entrades virtuals I²C i registres de sortida ASM. Tal com es descriu a la nota d'aplicació AN-1090 Controladors IOC simples I²C amb SLG46531V (vegeu la nota d'aplicació AN-1090 Controladors IOC simples I²C amb SLG46531V, Dialog Semiconductor), l'ordre d'escriptura I²C s'estructura de la següent manera:

● Inici;

● Byte de control (el bit R / W és 0);

● Adreça de paraula;

● Dades;

● Atureu-vos.

Totes les ordres d'escriptura I²C es fan a Word Address 0xF4 (entrades virtuals I²C) i 0xD0 (sortida ASM per a l'estat 0). Les ordres per escriure a IC1 i controlar els dígits 1 i 2 de la pantalla LCD es resumeixen a la taula 3. A la representació de la seqüència d'ordres, el claudàtor obert "[" indica el senyal d'inici i el claudàtor "]" indica el senyal d'aturada.

Els dos bytes anteriors controlen els segments del dígit LCD 1 i del dígit 2 junts. Aquí, l'enfocament consisteix a utilitzar una taula de cerca individual (LUT) en programari per a cada dígit, tenint en compte els segments en ambdós bytes. Els valors de bytes de la taula de cerca s'han de barrejar mitjançant una operació OR de bits i, a continuació, enviar-los a l'IC. A la taula 4 es mostren els valors Byte0 i Byte1 per a cada valor numèric que s’hauria d’escriure a cada dígit de visualització.

Per exemple, per escriure al dígit 1 el número 3 i al dígit 2 el número 4, el byte0 és 0xBD (0x8D OR a bit amb 0xB0) i el byte 1 és 0x33 (0x30 a bit a bit OR amb 0x03).

La comanda per escriure a IC2 i els controls del dígit 3 i 4 es descriu a la taula 5.

La lògica de control dels dígits 3 i 4 és com el control dels dígits 1 i 2. La taula 6 mostra el LUT d’aquests dos dígits.

La diferència en IC2 és el segment COL. Aquest segment està controlat per Byte1. Per configurar aquest segment a les fosques, s'hauria de fer una operació OR a bit entre el Byte1 i el valor 0x40.

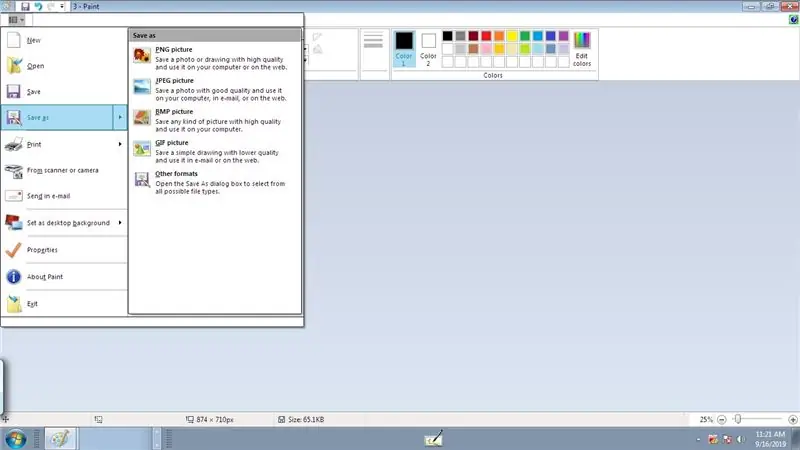

Pas 11: ordres I²C per a la prova LCD

Per a la prova LCD es va desenvolupar un firmware en llenguatge C per a la placa MCU. Aquest microprogramari enviarà una seqüència d’ordres als dos circuits integrats del tauler de control. El codi font d’aquest firmware es troba a la secció Apèndix. Tota la solució es va desenvolupar mitjançant Atollic TrueStudio for STM32 9.0.1 IDE.

La seqüència d’ordres i els valors respectius que es mostren a la pantalla es resumeixen a la Taula 7 anterior.

Pas 12: Resultats de les proves

La prova del prototip consisteix en verificar els valors de visualització després d'una ordre MCU i mesurar el dissipador actual per cada IC durant l'operació.

Les imatges de la pantalla LCD per a cada valor de l'ordre es mostren a la taula 8 anterior.

La pica actual per a cada dispositiu es va mesurar amb un multímetre, en el seu rang de corrent més baix de 200 µA. Les imatges del corrent mesurat per a cada dispositiu, durant l’arrencada i el funcionament normal, es mostren a la taula 9 anterior.

Conclusió i debat sobre els resultats

Es va presentar el disseny d’un controlador LCD estàtic de baixa potència amb dispositiu GreenPAK. Aquest disseny mostra clarament una de les principals característiques dels dispositius GreenPAK: el seu baix corrent en repòs. Com que els dispositius GreenPAK són una solució basada en maquinari, és possible treballar en una operació de baixa freqüència, en aquest cas de 48 Hz. Una solució basada en MCU requerirà una freqüència d’operació més alta, fins i tot per períodes de temps periòdicament curts, i després obtindrà més energia. I, comparant el dispositiu GreenPAK amb un CPLD (Complex Programmable Logic Device), és clar veure que normalment un CPLD té un corrent en repòs superior a 20 µA.

És interessant notar que aquest disseny es podria modificar fàcilment per adaptar-se millor als requisits d’un projecte específic. Un bon exemple és el pinout de controls de segments. Es podrien canviar fàcilment per simplificar la placa de circuits impresos i el desenvolupament de programari alhora. Aquesta és una característica interessant quan es compara el dispositiu amb un ASIC (Circuit integrat específic d’aplicació). Normalment, els ASIC estan dissenyats per adaptar-se a una àmplia gamma d’aplicacions i s’hauria d’escriure una rutina inicial de programari per configurar correctament l’IC abans de l’operació. Es podria dissenyar un dispositiu configurable per començar a estar preparat per utilitzar-se després de l’encesa. D’aquesta manera, és possible reduir el temps de desenvolupament de programari per a la configuració inicial de l’IC.

El codi font de l'aplicació es troba aquí a l'Apèndix A.

Recomanat:

Introducció a la interfície del sensor I2C ?? - Interfície del MMA8451 mitjançant ESP32: 8 passos

Introducció a la interfície del sensor I2C ?? - Interfície del MMA8451 mitjançant ESP32s: en aquest tutorial, aprendreu tot sobre com iniciar, connectar-se i aconseguir que el dispositiu I2C (acceleròmetre) funcioni amb el controlador (Arduino, ESP32, ESP8266, ESP12 NodeMCU)

SCARA Robot: Aprendre sobre Foward i la cinemàtica inversa !!! (Plot Twist Aprèn a fer una interfície en temps real a ARDUINO mitjançant PROCESSAMENT !!!!): 5 passos (amb imatges)

SCARA Robot: Aprendre sobre Foward i la cinemàtica inversa !!! (Plot Twist Aprèn a fer una interfície en temps real a ARDUINO mitjançant el processament !!!!): Un robot SCARA és una màquina molt popular al món de la indústria. El nom significa tant el braç de robot de muntatge selectiu que compleix com el braç de robot articulat que compleix selectivament. Bàsicament és un robot de tres graus de llibertat, sent els dos primers desplaçaments

ESP8266 IP estàtic (WIP): 3 passos

ESP8266 IP estàtic (WIP): (Si la vostra xarxa Wi-Fi ja està configurada d'alguna manera, és possible que hàgiu de parlar amb l'administrador de la vostra xarxa.) Part de l'objectiu del nostre projecte és assignar a cada ESP8266 la seva pròpia adreça IP estàtica a faciliteu el seguiment dels dispositius i la connexió

Tutorial Arduino LCD 16x2 - Interfície de pantalla LCD 1602 amb Arduino Uno: 5 passos

Tutorial Arduino LCD 16x2 | Interfície de pantalla LCD 1602 amb Arduino Uno: Hola nois, ja que molts projectes necessiten una pantalla per mostrar les dades tant si es tracta d’un comptador de bricolatge com de pantalla de comptadors de subscripcions a YouTube o una calculadora o un pany de teclat amb pantalla i si tot aquest tipus de projectes es fan amb arduino definitivament

Tutorial Com fer una interfície de visualització de 4 dígits amb Arduino UNO: 6 passos (amb imatges)

Tutorial Com fer una interfície de visualització de 4 dígits amb Arduino UNO: aquest tutorial us ensenyarà alguns conceptes bàsics sobre l'ús de la pantalla de 4 dígits amb Arduino UNO