Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:13.

- Última modificació 2025-01-23 14:37.

El nostre objectiu amb aquest projecte era crear alguna cosa que estalviés recursos energètics i financers a les comunitats. Els llums públics activats per moviment farien aquestes dues coses. A tota la nació s’està malgastant l’energia en els llums dels carrers que il·luminen carrers buits. El nostre sistema d’il·luminació pública garanteix que els llums només s’encenguin quan sigui necessari i estalvia innombrables dòlars a les comunitats. Mitjançant sensors de moviment, el sistema encén els llums només quan hi ha cotxes. També per a la seguretat dels vianants, vam implementar un botó d’anul·lació que encén tots els llums del carrer. Els passos següents us guiaran per com hem dissenyat i construït el nostre model reduït del projecte mitjançant Vivado i una placa Basys 3.

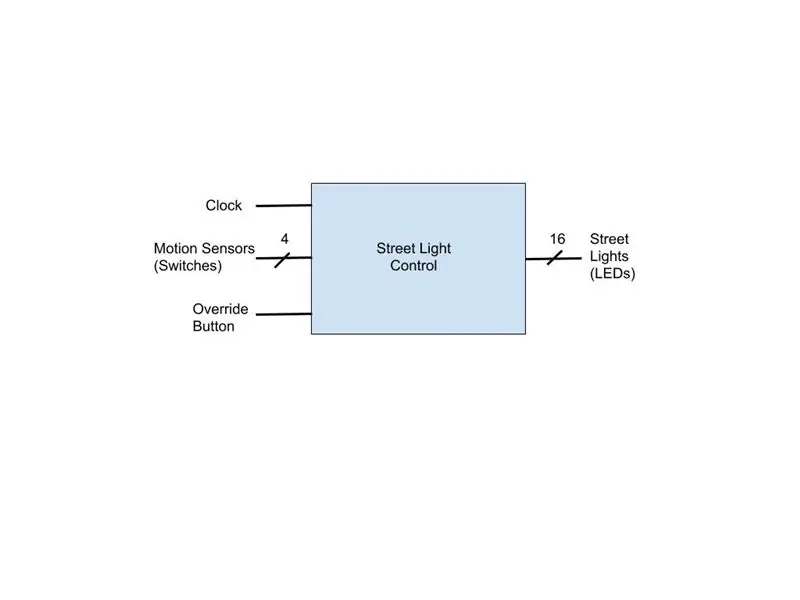

Pas 1: Sistema Black Box

Vam començar aquest projecte dibuixant un senzill diagrama de caixa negra. Un diagrama de quadre negre simplement mostra les entrades i sortides que requereix el nostre sistema per completar tots els processos necessaris. Hem intentat que el nostre disseny sigui el més senzill i bàsic possible. Les nostres entrades del sistema inclouen un bus de sensors de moviment (4 per al nostre model reduït), un botó d’anul·lació de vianants i una entrada de rellotge. A l'altre costat, la nostra única sortida és un autobús de llums LED que representen els nostres llums públics. Per a aquest model, hem utilitzat un escenari de 16 llums de carrer simplement perquè aquest és el nombre màxim de sortides LED incorporades a la placa Basys 3. Finalment, mitjançant aquest diagrama vam poder crear els nostres fitxers de projecte, font i restricció de Vivado amb entrades i sortides adequades.

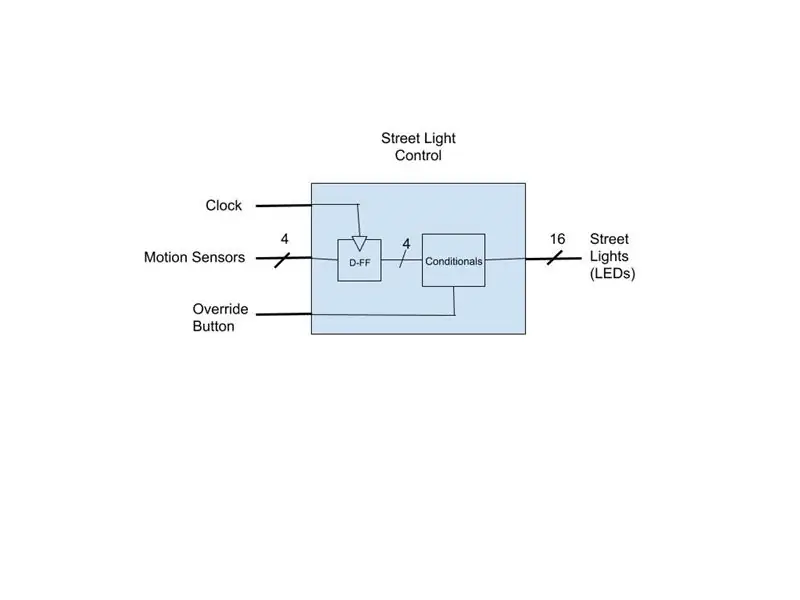

Pas 2: components

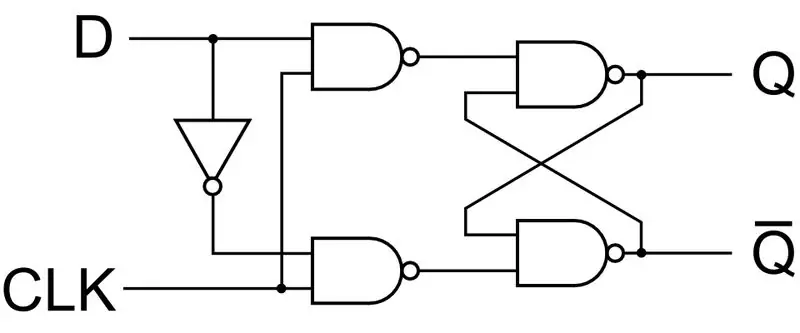

En aquest pas, aprofundim examinant els components que formen el nostre diagrama de caixa negra. El nostre primer component és un fitxer font VHDL que conté D xancles. Les xancletes D simplement agafen qualsevol senyal que se’ls introdueix des dels sensors situats a la vora ascendent del rellotge i bloqueja aquestes dades fins a la següent vora ascendent. Això evita que els nostres sensors de moviment sensibles facin que els LED de sortida "parpellegin". A més, posem una sola xancla D al senyal d’entrada del botó per mantenir els LED encesos durant uns 5-7 segons després de prémer el botó. També ho vam fer mitjançant un divisor de rellotge.

l'entitat clk_div2 és Port (clk: in std_logic; sclk: out std_logic); final clk_div2;

l'arquitectura my_clk_div de clk_div2 és

constant max_count: enter: = (300000000); senyal tmp_clk: std_logic: = '0'; begin my_div: process (clk, tmp_clk) variable div_cnt: enter: = 0; començar if (rising_edge (clk)) llavors if (div_cnt = MAX_COUNT) llavors tmp_clk <= no tmp_clk; div_cnt: = 0; else div_cnt: = div_cnt + 1; acabar si; acabar si; sclk <= tmp_clk; finalitza el procés my_div; acabar my_clk_div;

El nostre component final en aquest diagrama és un fitxer font de comportament VHDL que conté condicionals per a les sortides basades en la configuració de senyals d’entrada.

Pas 3: D Xancles

Les quatre xancletes connectades als senyals d’entrada són essencials per a la funcionalitat del nostre sistema. Com s’ha dit anteriorment, amb sensors de moviment sensibles i un botó d’anul·lació, les xancletes utilitzen pestells per generar només el nostre senyal d’entrada a la vora ascendent del rellotge. Aquesta lògica seqüencial significa que els nostres llums públics poden romandre encesos durant un determinat període de temps després d’haver estat activats per un moviment ràpid. La codificació d'un D-Flip Flop és bastant senzilla:

beginprocess (CLK) comença si rising_edge (CLK) llavors Q <= D; acabar si; finalitzar el procés;

Tot es pot compilar en una única sentència if. Un cop vam tenir aquesta peça, vam crear un fitxer font estructural de VHDL que contenia els quatre xancletes necessaris:

començar DFF0: mapa de ports DFF (CLK => CLK, D => D (0), Q => Q (0)); DFF1: mapa de ports DFF (CLK => CLK, D => D (1), Q => Q (1)); DFF2: mapa de ports DFF (CLK => CLK, D => D (2), Q => Q (2)); DFF3: mapa de ports DFF (CLK => CLK, D => D (3), Q => Q (3));

final Conductual;

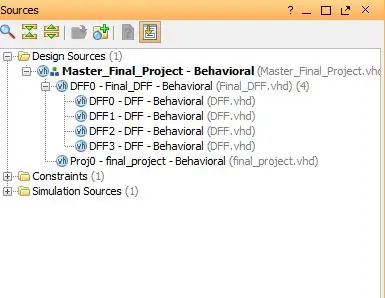

Això ajuda a mantenir el nostre fitxer estructural principal on reunim tots els components del sistema molt més nets i organitzats.

Pas 4: Condicionals

Per tal de mantenir el nostre codi compacte i eficaç, vam escriure tots els nostres condicionants en un sol cas. Per al nostre model reduït, teníem 16 possibles configuracions de sortida de LED, ja que cada sensor de moviment és responsable d’un grup de 4 LED.:

el cas NMS és quan "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; cas final;

Pas 5: restriccions

Per tal d’establir correctament les vostres entrades i sortides mitjançant Vivado, heu d’implementar un fitxer de restricció que indiqui tots els ports, botons, LEDs i rellotges que s’utilitzen.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [1]}] U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property PACKAGE_PIN W18 get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE_PIN U14 [get_ports LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 [get_ports {LED 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] set_property IO LVCMOS33 ESTÀNDARD [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11]}] set_Verty IOST [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [13]}] {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCMOS33 [get_ports { [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [1]}] B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

Pas 6: fitxer font principal

En aquest fitxer principal reunim tots els fitxers font dels components esmentats anteriorment. Aquest fitxer funciona com a codi estructural que reuneix els components dispars.

entitat Master_Final_Project és Port (BTN: a STD_LOGIC; CLK: a STD_LOGIC; MS: a STD_LOGIC_VECTOR (3 a 0); LED: a STD_LOGIC_VECTOR (15 a 0)); final Master_Final_Project;

arquitectura El comportament del Projecte_Final_Mestre és

component final_project is Port (--CLK: in STD_LOGIC; NMS: in STD_LOGIC_VECTOR (3 downto 0); BTN: in STD_LOGIC; --sw: in STD_LOGIC_Vector (1 downto 0); LED: out STD_LOGIC_VECTOR (15 downto 0)); component final;

el component Final_DFF és

Port (CLK: en STD_LOGIC; D: en STD_LOGIC_Vector (3 fins a 0); Q: fora STD_LOGIC_Vector (3 fins a 0)); component final;

senyal DFF02proj30: STD_LOGIC;

senyal DFF12proj74: STD_LOGIC; senyal DFF22proj118: STD_LOGIC; senyal DFF32proj1512: STD_LOGIC;

començar

DFF0: Mapa de ports Final_DFF (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: mapa de ports final_project (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); final Conductual;

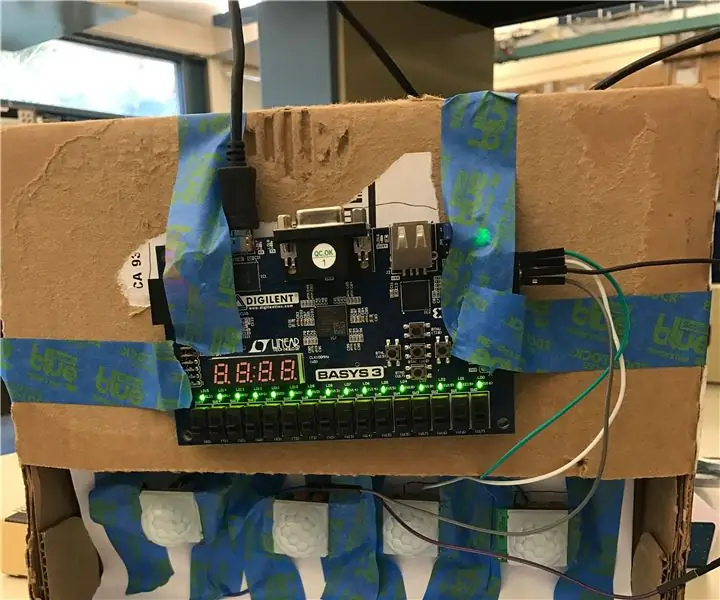

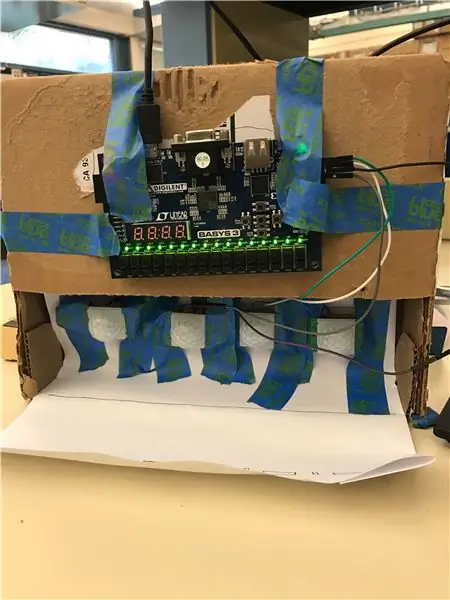

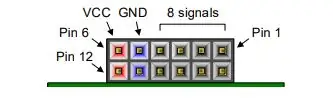

Pas 7: Muntatge

El muntatge de maquinari d’aquest projecte és mínim. Les úniques peces necessàries són les següents:

1. Tauler Basys 3 (1)

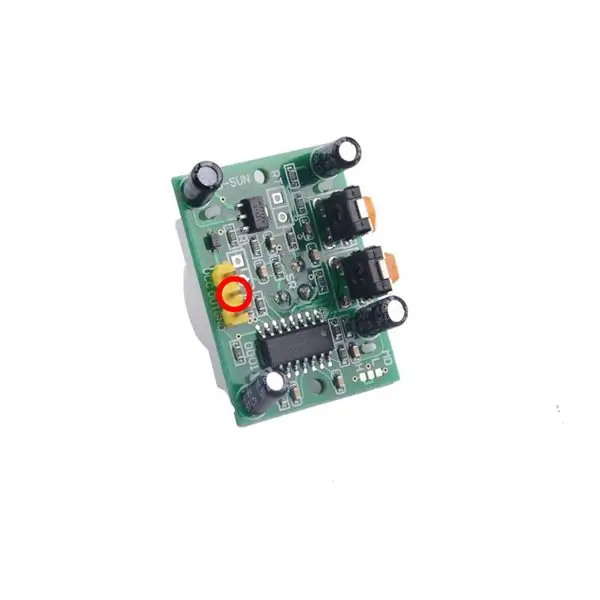

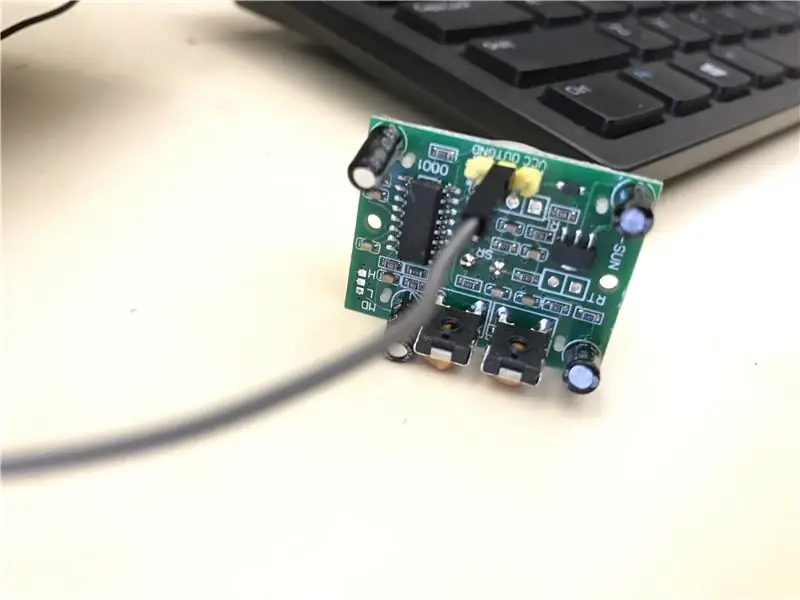

2. Sensors de moviment barats que es poden trobar a Amazon aquí. (4)

3. Conduccions entre homes i dones (4)

Muntatge:

1. Connecteu 4 cables masculins als ports 1-4 JB de la capçalera PMod (vegeu la figura).

2. Connecteu els extrems femelles al pin de sortida de cada sensor de moviment.

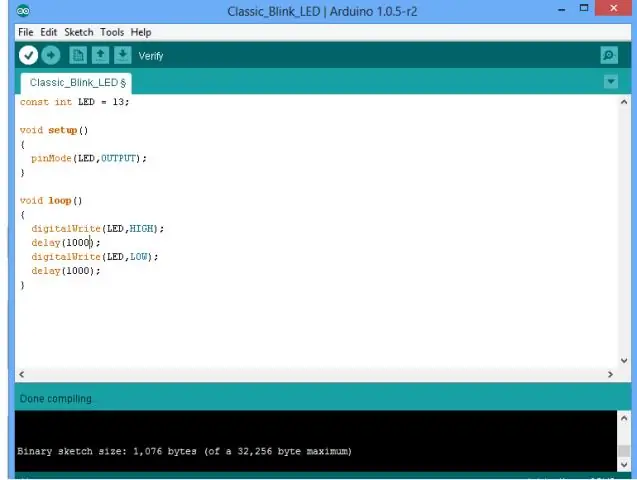

Pas 8: carregar el programa

Ara estem preparats per carregar el fitxer font mestre VHDL a la placa Basys 3. Assegureu-vos d'executar la síntesi, la implementació i generar la comprovació de flux de bits per si hi ha possibles errors. Si tots s’executen correctament, obriu el gestor de maquinari i programa el dispositiu Basys 3. El vostre projecte ja està complet.

Recomanat:

LED activats per veu: 8 passos

LEDs activats per veu: Webduino utilitza el navegador d’Internet Chrome per controlar tot tipus de components electrònics, de manera que hauríem de poder utilitzar la resta de funcions que Chrome us ofereix. En aquest exemple de projecte utilitzarem l'API de veu de Chrome. S’utilitza el reconeixement de veu de Google

Fanals posteriors seqüencials: 7 passos

Fanals posteriors seqüencials: aquest instructiu mostra com codificar i connectar una seqüència de LED similars als intermitents d’emergència d’un Mercury Cougar de 1969. Els llums posteriors seqüencials van aparèixer en diversos cotxes dels anys seixanta i principis dels setanta i van ser portats al Ford Mustang per

Electrodomèstics activats per veu mitjançant Alexa: 9 passos (amb imatges)

Electrodomèstics activats per veu mitjançant Alexa: la unitat desenvolupada aquí fa que els vostres electrodomèstics com ara televisors, amplificadors, reproductors de CD i DVD controlin amb ordres de veu mitjançant Alexa i Arduino. L’avantatge d’aquesta unitat és que només heu de donar ordres de veu. Aquesta unitat pot funcionar amb tots els aparells que

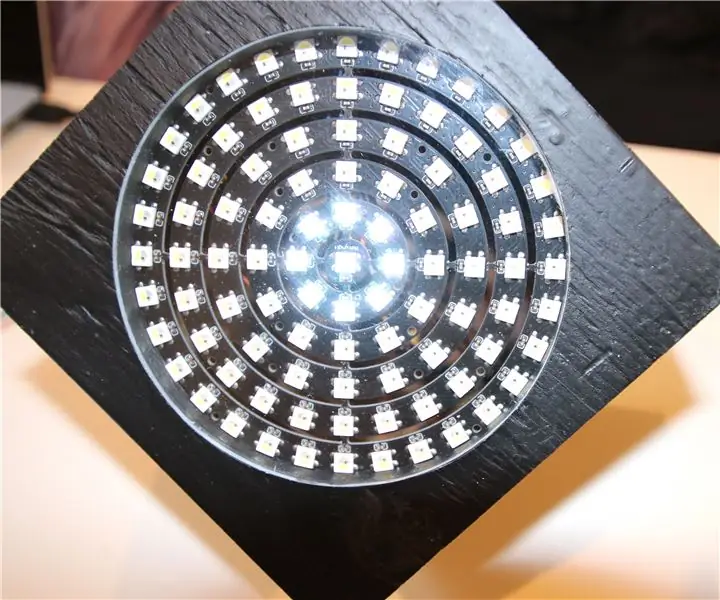

Pols (LED activats per volum): 7 passos (amb imatges)

Pulse (LED activats per volum): alguna vegada heu volgut crear alguna cosa amb LED, però no sabíeu per on començar? Aquesta guia us proporcionarà alguns passos senzills per dissenyar el vostre propi codi de visualització de volum per a llums LED adreçables. Es tracta d'un divertit mesurador de soroll d'escriptori, rave de

LED intermitents activats per llum: 4 passos

LED parpellejadors activats per llum: en aquest instructiu us mostraré com muntar un circuit LED intermitent que s’encengui quan l’agiteu amb la mà, parpelleja durant un segon o dos i després s’esvaeix. He rebut l’esquema del circuit intermitent de les instruccions de steven123654