Taula de continguts:

- Pas 1: afegiu fonts i trieu "Afegeix o crea fonts de simulació

- Pas 2: Creeu un fitxer anomenat Enable_sr_tb

- Pas 3: Creeu un fitxer Testbench

- Pas 4: definiu Enable_sr_tb com a nivell superior sota la simulació

- Pas 5: executeu la síntesi i la simulació de comportament

- Pas 6: avalueu el resultat de la simulació

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:15.

- Última modificació 2025-01-23 14:38.

He fet aquest projecte de simulació per a una classe en línia. El projecte està escrit per Verilog. Utilitzarem la simulació a Vivado per visualitzar la forma d'ona a enable_sr (dígit d'activació) a partir del projecte de cronòmetre creat anteriorment. A més, farem servir la tasca del sistema per mostrar els errors comesos per nosaltres en el disseny.

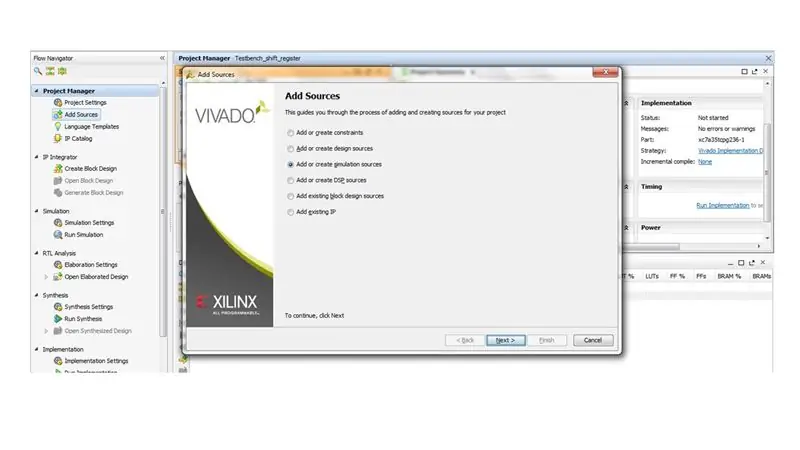

Pas 1: afegiu fonts i trieu "Afegeix o crea fonts de simulació

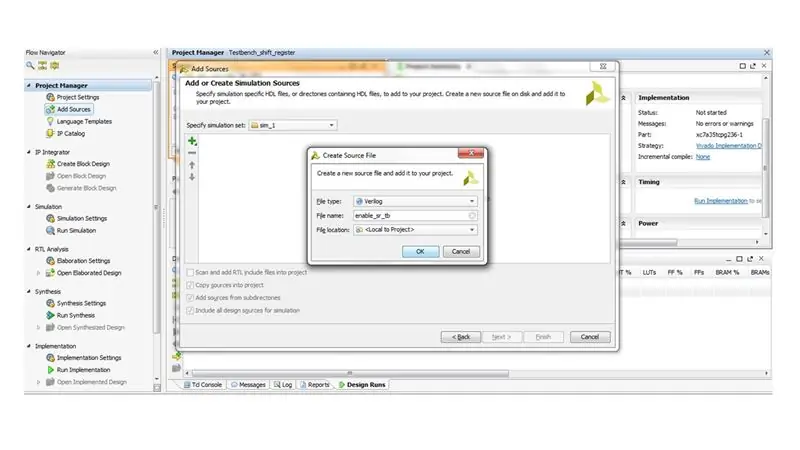

Pas 2: Creeu un fitxer anomenat Enable_sr_tb

Pas 3: Creeu un fitxer Testbench

1. Importeu el mòdul enable_sr des del projecte de cronòmetre. Aquest és el fitxer que volem simular

2. Creeu el mòdul testbench enable_sr_tb ();

3. Introduïu entrades i sortides del mòdul enable_sr (). Recordeu que les entrades de enable_sr ara són de tipus registre mentre que les sortides es converteixen en tipus de xarxa.

4. Instanteu la unitat en prova (uut) que és enable_sr

5. Generar un rellotge quin període (T) és de 20ns

6. Utilitzeu la sentència condicional per crear un sistema de comprovació d'errors. En aquest exemple, volem comprovar si hi ha més d'un dígit actiu.

Nota: al fitxer enable_sr () original, hauríem d’inicialitzar el patró com a 4’b0011 perquè hi hagi dos dígits actius per crear error

7. Utilitzeu la tasca del sistema $ display per mostrar l'error

8. Utilitzeu la tasca del sistema $ finish per completar la simulació a 400ns de temps

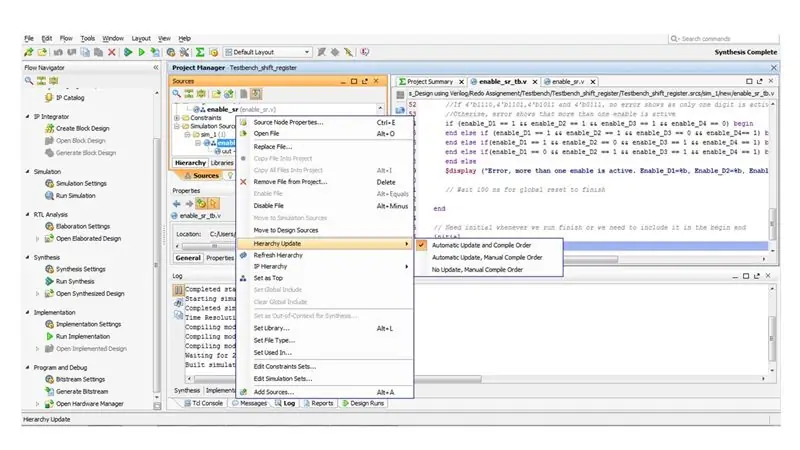

Pas 4: definiu Enable_sr_tb com a nivell superior sota la simulació

Pas 5: executeu la síntesi i la simulació de comportament

- Abans d'executar la simulació de comportament, executeu la síntesi per assegurar-vos que no hi hagi errors de sintaxi al fitxer testbench i a la unitat sota el fitxer de prova.

- Executeu la simulació de comportament

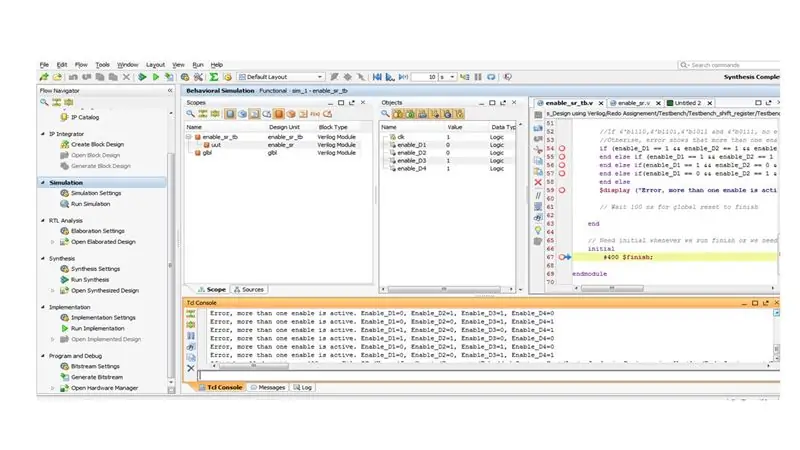

Pas 6: avalueu el resultat de la simulació

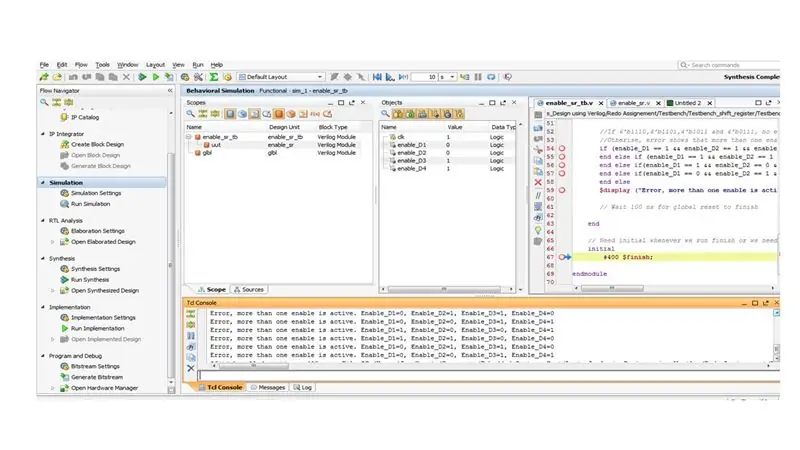

Veureu les finestres de simulació. Conté diferents panells.

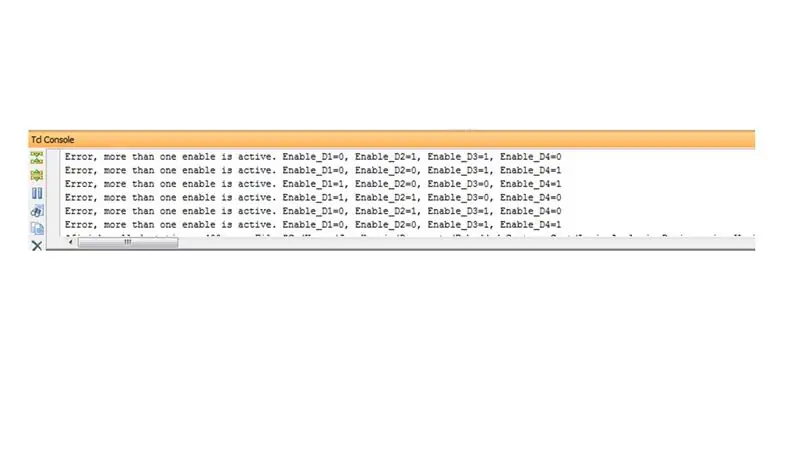

Veureu el missatge d'error al tauler de la consola. Això mostra que hi ha més d’un dígit actiu durant el període de simulació.

També podeu veure la forma d'ona a l'abast

S'adjunta el fitxer del projecte.

Recomanat:

Arduino Com utilitzar la pantalla OLED d'1,3 polzades SH1106: 7 passos

Com fer servir Arduino Pantalla OLED de 1,3 polzades SH1106: en aquest tutorial aprendrem a utilitzar un programari OLED de 1,3 polzades SH1106 Arduino i Visuino. Mireu el vídeo

[2020] Utilitzar l’aplicació Game Pad d’iPhone o iPad i Micro: bit per controlar un cotxe RC: 23 passos

![[2020] Utilitzar l’aplicació Game Pad d’iPhone o iPad i Micro: bit per controlar un cotxe RC: 23 passos [2020] Utilitzar l’aplicació Game Pad d’iPhone o iPad i Micro: bit per controlar un cotxe RC: 23 passos](https://i.howwhatproduce.com/images/001/image-1423-j.webp)

[2020] Ús de l’aplicació Game Pad d’iPhone o iPad i Micro: bit per controlar un cotxe RC: heu pensat a utilitzar el vostre iPhone o iPad per controlar el vostre micro: bit? Sabeu que Micro: bit Educational Foundation proporciona l’aplicació iOS a la Tenda d'aplicacions? Cerca " micro: bit " a l’App Store i podeu descarregar-la de forma gratuïta. El

Com configurar un Raspberry Pi i començar a utilitzar-lo: 4 passos

Com configurar un Raspberry Pi i començar a utilitzar-lo: per als lectors del futur, som al 2020. L’any en què, si teniu la sort d’estar sa i no estar infectat per Covid-19, de cop i volta, , tinc molt més temps lliure del que mai imaginaves. Llavors, com puc ocupar-me d’una manera no massa estúpida? Ah, sí

Com utilitzar el motor pas a pas com a codificador rotatiu i pantalla OLED per a passos: 6 passos

Com utilitzar el motor pas a pas com a codificador rotatiu i pantalla OLED per als passos: en aquest tutorial aprendrem com fer un seguiment dels passos del motor pas a pas a la pantalla OLED. Mireu un vídeo de demostració. El crèdit per al tutorial original va a l'usuari de youtube " sky4fly "

Síntesi de blocs de vídeo IP de Vivado HLS: 12 passos

Síntesi de blocs IP de vídeo Vivado HLS: alguna vegada heu volgut processar en temps real el vídeo sense afegir molta latència o en un sistema incrustat? De vegades s’utilitzen FPGA (Field Programmable Gate Arrays); tanmateix, escrivint algoritmes de processament de vídeo a l'especificació de maquinari