Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:11.

- Última modificació 2025-01-23 14:37.

JDM és un popular programador PIC perquè utilitza un port sèrie, un mínim de components i no necessita alimentació. Però hi ha confusió, amb moltes variacions de programador a la xarxa, quins funcionen amb quins PIC? En aquest "instructable" posem a prova JDM i demostro com simular el circuit amb Spice, que respondrà a totes les vostres preguntes.

Subministraments

LTspice que es pot descarregar des de Analog Devices aquí.

Aquí també necessiteu els fitxers del circuit JDM.

Pas 1: Requisits del port sèrie

JDM requereix un port sèrie que compleixi les especificacions EIA232, idealment amb nivells de tensió + 12 / -12.

Segons el full de dades de Texas Instruments Line Driver MC1488 (Figura 3)

Impedància de sortida = 4V / 8mA = 500 ohm.

Límit de corrent de curtcircuit = 12 mV, sense límit de temps, sense danys al xip.

Impedància d'entrada del receptor de línia = 3k a 7k ohm recomanat.

Els ports sèrie en ordinadors de sobretaula antics fan servir + 12v / -12V que compleixen aquest requisit.

Els ports sèrie dels ordinadors portàtils més nous utilitzen tensions més baixes. JDM pot funcionar o no; la resposta és més complexa.

Pas 2: Requisits de programació PIC

La informació sobre els requisits de programació PIC s’obté de Microchip. L'anterior és per a un dispositiu típic.

Pas 3: Especificació de JDM

S’ha perdut el lloc web original de JDM en el temps? Això ens deixa endevinar què pretenia originalment el dissenyador per a l'especificació.

- Proporcioneu VDD = 5V i fins a IDD = 2mA màxim (per a la versió "in socket")

- Proporcioneu VHH = 13V i fins a IHH = 0,2 mA màxim.

- MCLR Temps d'augment tVHHR = 1uS màx.

- La versió ICSP ha de ser capaç de baixar MCLR contra 22k pull-up a l'objectiu.

Pas 4: Descripció del circuit

La figura JDM1 es basa en el circuit JDM "estàndard" extret del lloc web PICPgm. Aquest és el programador "PIC in Socket" on el PIC pren energia dels pins TX i RTS. El diagrama original era difícil d’entendre, de manera que l’he redibuixat utilitzant la convenció normal del flux de corrent de dalt a baix. I he afegit indicadors LED "RESET", "PROG" i "RTS" que són necessaris durant la construcció i les proves. Esperem que no tinguin cap efecte perjudicial sobre el comportament.

La convenció normal del disseny de circuits és habitual, però la característica clau de JDM és que la terra del port sèrie (GND) està connectada a VDD. Això crea confusió a mesura que els senyals de port sèrie es mesuren respecte a GND, senyals PIC respecte a terra lògica (VSS).

Quan TX augmenta, Q1 es comporta com dos díodes esbiaixats cap endavant. (El col·lector Q1 no està esbiaixat inversament com passa amb el transistor normal). El col·lector Q1 carrega C2, que està fixat a VDD + 8V per Zener (D3). L'emissor Q1 proporciona 13V a MCLR per al mode de programa / verificació.

Quan TX baixa, el condensador C3 es carrega a través de D1 i VSS es fixa a VDD-5V per zener (D5). També el TX està fixat a (VSS-0.6) per D1. Q1 està apagat, C1 manté la seva càrrega pel següent impuls de programació. El MCLR està fixat a 0V per D2, de manera que el PIC s'ha reinicialitzat.

Quan RTS és alt, el rellotge es transmet a PGC. D4 clamp PGC a la lògica VDD alta. Quan RTS és baix, el condensador C3 es carrega a través de D6 i VSS es fixa a VDD-5V per zener (D5). D6 abraça PGC a VSS o lògica 0.

Durant la programació, les dades enviades a DTR es llegeixen a PGD, que el PIC configura com a entrada. Quan el DTR és alt, Q2 actua com a "seguidor de l'emissor" i el voltatge PGD és aproximadament (VDD-0.6) o lògic 1. Quan el DTR és baix, Q2 actua com un transistor defectuós (emissors i pins de col·lector invertits). Q2 fa baixar el PGD, que està fixat per D7 a VSS o a la lògica 0.

Durant la verificació, el PIC configura PGD com a sortida per enviar dades al port sèrie. Cal establir DTR com a alt i les dades es llegeixen a CTS. Quan la sortida PGD és alta, Q2 està desactivat, CTS = DTR = + 12V. Quan la sortida PGD és baixa, Q2 està activat. El col·lector Q2 treu corrent (12V + 5V) / (1k + 1k5) = 7mA de DTR i fa baixar CTS a VSS.

Pas 5: prepareu-vos per a la simulació

Descarregueu LT spice, deseu i obriu els fitxers del circuit (*.asc) que es proporcionen aquí. Per simular el circuit, li hem de donar algunes entrades i després "rastrejar" les sortides. V1, V2 V3 simula el port sèrie de 12V amb impedància de sortida R11, R12, R13.

- V1 genera 2 impulsos de programa a TX des de 0,5 ms fins a 4,5 ms

- V2 genera ràfegues de polsos de dades en DTR d’1,5 a 4,5 ms

- V3 genera ràfegues d’impulsos de rellotge a RTS de 0,5 a 3,5 ms

Els components V4, X1, R15 i R16 formen part de la simulació.

- V4 genera 2 polsos de 2,5 a 4,5 ms per verificar les dades.

- Jumper X1 simula OUTPUT en PGD.

- R15, R16 simulen la "càrrega" de PIC en VDD i MCLR.

Pas 6: modificacions per a ICSP

La figura JDM3 mostra la versió per a la programació "en circuit". Les modificacions de l'original són

- Substituïu el sòcol ZIF per un connector ICSP.

- El PIC ara s’alimenta mitjançant l’alimentació al circuit objectiu (V5).

- Traieu el zener de 5V (D5).

- El petit condensador 100pF (C4) es mou al costat del PIC al circuit objectiu.

- Els LED prenen alimentació de la placa de circuits sempre que sigui possible.

- Es requereixen la resistència de tracció MCLR (R10) i el díode (D10) al circuit objectiu.

- AVÍS. La placa de destinació ha de tenir un subministrament “flotant”, idealment una bateria.

- No connecteu la terra de destinació (VSS) a la terra de l'ordinador / PC connectant cap altre port d'ordinador al mateix temps que JDM.

Després de simular JDM1, es va fer evident el problema del temps de càrrega llarg a C2. Després de llegir Fruttenboel, sembla que es van afegir C2 i Q1 com a modificació de l'original. No puc pensar què pretén fer C2 i Q1 a part de crear problemes. Per tant, per a JDM4, tornem al disseny anterior de Fruttenboel, que és senzill i senzill d’entendre. Pinça MCLR D1 i D3 / LED2 entre VSS i VDD + 8V. El valor de R1 es redueix a 3k3, només suficient per il·luminar el LED2 a 12V.

JDM4 també està dissenyat per treballar amb ports sèrie més febles. Quan el TX augmenta (+ 9V), la font de corrent TX = (9-8) / (1k + 3k3) = 0,2 ma, prou com per augmentar la MCLR, tot i que insuficient per il·luminar el LED2. Quan TX baixa (aproximadament -7V), el corrent de TX s'enfonsa = (9-7) / 1k = 2mA. Corrent LED1 = (7-2 per a led) / (2k7) = 1,8 mA. Corrent de baixada de MCLR = 7-5,5 / 3k3 = 0,5 mA.

Aquest circuit també s'ha provat (simulació JDM5) per veure què passa amb els ports sèrie +/- 7V mínim, on hi ha una tensió insuficient per mantenir VHH = 13V. El propòsit de C1 ara es fa evident, C1 crea un impuls curt + ve a MCLR, una pujada de 33us a la vora ascendent de TX, prou llarga perquè el PIC entri en mode de programació, potser? Però traieu el pont X2 (inhabiliteu el LED1), ja que no hi ha prou corrent per baixar el MCLR i il·luminar el LED1 junt. Quan TX baixa, l’enfonsament de corrent TX = (7V-5.5V) / (1k + 3k3) = 0,3mA, només és suficient per fer baixar l’MCLR contra el pull-up R10.

Pas 7: Resultats de simulació

Per veure els fitxers gràfics, és millor fer clic amb el botó dret als enllaços següents i seleccionar "Obre l'enllaç a la pestanya nova".

Simulació 1: traça de MCLR, VSS i RTS per a JDM1 original. Immediatament l’observació 1, 2 i 3 és evident.

Simulació 2: traça de MCLR i VSS i RTS per a JDM2 modificat, que soluciona problemes anteriors.

Simulació 3: traça de PGD, VSS i PGC per a l'enviament de dades de JDM2 en mode programa. Observació 4 a 3,5 mS.

Simulació 4: traça de PGD, VSS i CTS per a JDM2 en mode de verificació (jumper X1 inserit). D'acord

Simulació 5: traça de MCLR, VSS, PGD i PGC per a JDM3. ICSP que utilitza la potència del circuit resol molts problemes.

Simulació 6: traça de MCLR, VSS, PGD i PGC per a JDM4 amb port sèrie +/- 9V. MCLR augmenta immediatament, funcionant completament.

Simulació 7: traça d'MCLR, VSS i TX per a JDM5 amb port sèrie +/- 7V i el pont X2 eliminat. C1 crea un augment de + ve (pujada) a la vora ascendent de MCLR, gairebé suficient per empènyer MCLR per sobre de TX fins a 13V.

Pas 8: Conclusions

Spice és molt bo per revelar "secrets ocults" del funcionament del circuit. Evidentment, el circuit JDM funciona i és compatible amb molts xips PIC, però les següents observacions revelen possibles limitacions / problemes de compatibilitat / errors?

- Temps de pujada llarg de MCLR mentre C2 es carrega a VPP al primer impuls de TX. Falla a l'especificació 3.

- El port sèrie carrega C2 quan TX augmenta i RTS baixa. Però RTS també té la feina de carregar C3. Quan tots dos es produeixen al mateix temps, això crea més càrrega a RTS, per tant C3 perd càrrega (augmenta el VSS) a 2 ms en la simulació. No es pot especificar 1.

- C3 perd la càrrega (el VSS comença a augmentar) després que els polsos del rellotge s’aturin a 3,5 ms.

- Quin és el propòsit de C2, és necessari?

Solucions

- Presumiblement, PICPgm utilitza un programari "de treball". Ha d'aplicar un pols TX llarg per precarregar-se a C2, i després només entrar al mode de programació després del segon impuls TX? Per a la simulació he reduït el valor de C2 a 1uF per donar un temps de pujada d'1 ms. No és una solució ideal.

- Dividiu C2 i C3 perquè es carreguin de forma independent. Una petita modificació de JDM2, C2, es fa referència a GND en lloc de VSS.

- Resolt per JDM3. ICSP és molt més fiable ja que el PIC funciona amb un circuit objectiu.

- JDM4 resol el problema 1. Aquest és un disseny senzill que elimina C2 del tot.

Pas 9: I finalment

La prova del púding està en el menjar. Aquest JDM funciona, així que seguiu utilitzant-lo.

I les meves recomanacions són:

- utilitzeu JDM2 per a la programació de sòcol i els ports sèrie de 12V,

- utilitzeu JDM4 per a programadors ICSP i ports sèrie superiors a +/- 9V,

- utilitzeu JDM4 amb el pont X2 eliminat per a ports sèrie superiors a +/- 7V.

Referències:

Dispositius analògics LT spice

picpgm

Fruttenboel

Seguiu més projectes PIC a sly-corner

Recomanat:

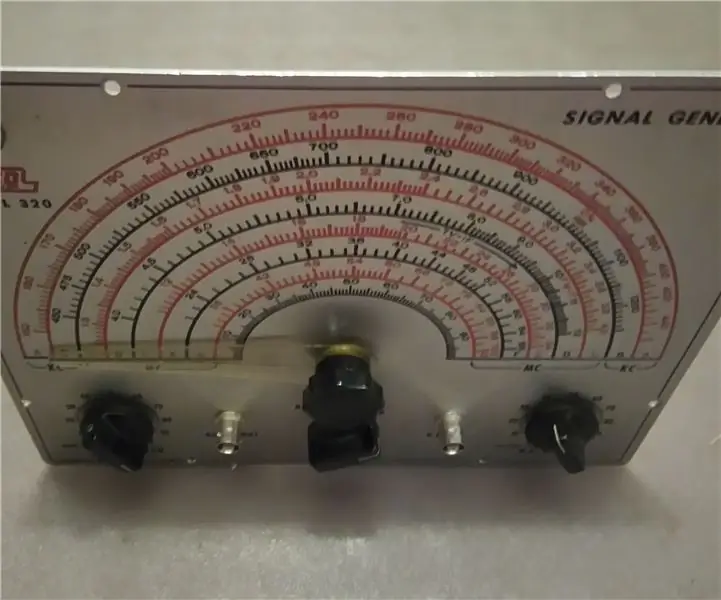

Revisió completa del generador de senyals vintage: 8 passos

Revisió completa del generador de senyals vintage: fa uns anys vaig adquirir un generador de senyal RF Eico 320 en una reunió de permutador de ràdio per un parell de dòlars, però fins ara no vaig fer res amb ell. Aquest generador de senyal té cinc rangs commutables de 150 kHz a 36 MHz i amb ha

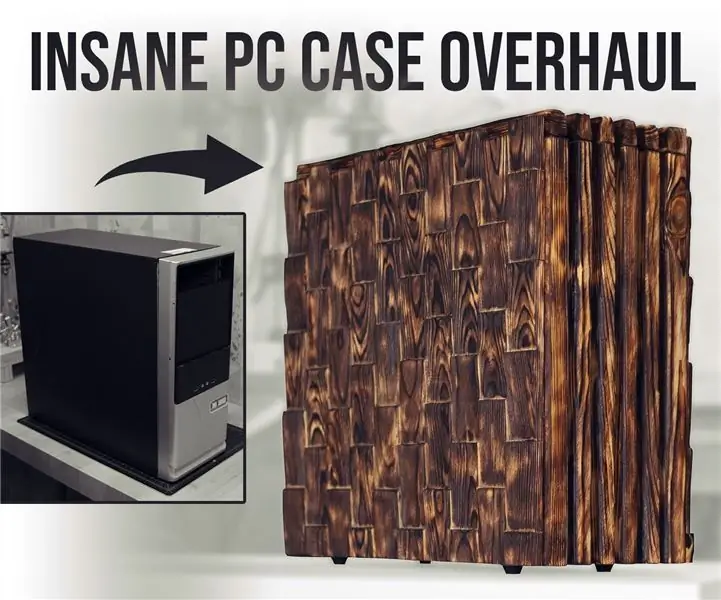

Revisió de casos de PC insana: 23 passos (amb imatges)

Revisió de casos insane de PC: en aquest vídeo / instructiu, faré una modificació relativament senzilla per obtenir un aspecte radicalment diferent per a un antic PC d’escriptori, però no només per l’aspecte. El flux d'aire per als components interiors també serà millor. I això permetrà que p

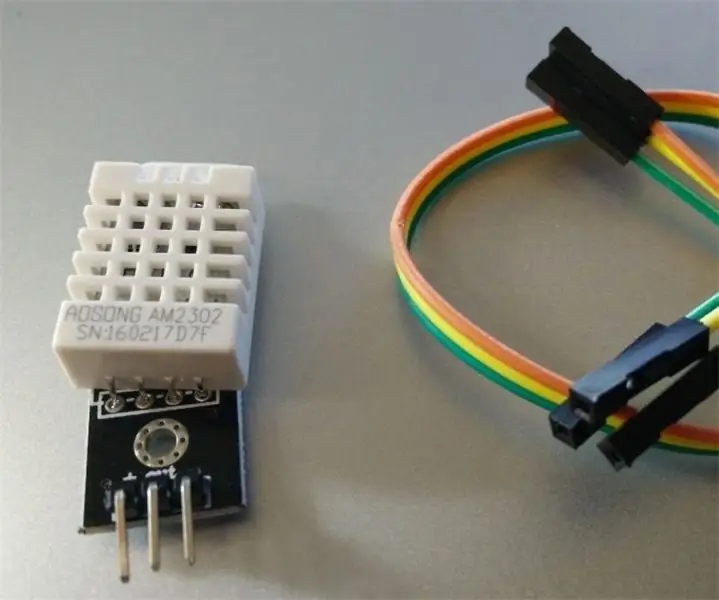

Més enllà de StandardFirmata: revisió: 5 passos

Més enllà de StandardFirmata: revisió: fa poc, el doctor Martyn Wheeler, usuari de pymata4, em va contactar per obtenir ajuda per afegir suport per al sensor d’humitat / temperatura DHT22 a la biblioteca pymata4. La biblioteca pymata4, juntament amb el seu homòleg Arduino, FirmataExpre

Reparació i revisió de l'obturador Olympus Pen-EE: 16 passos

Reparació i revisió de l'obturador Olympus Pen-EE: l'Olympus Pen-EE, des de l'any 1961, es pot desmuntar amb cura, netejar-se i revisar-lo i tornar-lo a muntar sense que hi hagi cap risc de perdre cap peça o danyar res a l'interior, si és útil , constant i pacient, i teniu l'eina adequada

Guia de revisió del producte portàtil Acer Extensa 5620: 12 passos

Guia de revisió del producte portàtil Acer Extensa 5620: el nostre petit Acer Extensa 5620 ens ha estat bo durant els darrers dos anys, eh? És una màquina prou agradable … però … tu també ho sents, oi? Funcionant una mica lent, el disc dur fa soroll, la bateria dura menys de vint minuts … és hora