Taula de continguts:

- Pas 1: diagrama de blocs

- Pas 2: Principi de funcionament

- Pas 3: Implementació de la lògica

- Pas 4: resoldre el punt mort

- Pas 5: Configuració del dispositiu: circuit Matrix0

- Pas 6: Configuració del dispositiu: lògica de rellotge SPI

- Pas 7: Configuració del dispositiu: propietats dels components de Matrix0

- Pas 8: Configuració del dispositiu: circuit Matrix1

- Pas 9: Configuració del dispositiu: comptador binari de 3 bits

- Pas 10: Configuració del dispositiu: lògica de comparació de 3 bits

- Pas 11: Configuració del dispositiu: lògica de comparació digital i registre temporal

- Pas 12: Configuració del dispositiu: propietats dels components de Matrix1

- Pas 13: Resultats

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:12.

- Última modificació 2025-01-23 14:37.

Els sistemes de control i els dispositius relacionats tracten múltiples fonts d’energia, com ara línies de polarització o bateries, i han de fer un seguiment de la línia més alta (o la més baixa) d’un conjunt determinat.

Per exemple, el canvi de càrrega en un sistema alimentat amb “diverses bateries” requereix que el sistema supervisi el voltatge mínim o màxim entre la matriu de bateries (màx o mínim en funció de l’algoritme de commutació particular) i encamini dinàmicament la càrrega cap al font més adequada en temps real. Com a alternativa, pot ser que el sistema hagi de desconnectar temporalment la bateria de baix voltatge per a una càrrega adequada.

Un altre exemple és el modern sistema d’energia solar, on cada panell solar està equipat amb un mecanisme de rotació inclinable i amb un circuit de seguiment solar (aquest últim proporciona la informació de posició solar per orientar el panell). Amb la informació de voltatge màxim, cada posició del panell solar es pot ajustar sobre la base de que el panell de la cadena realment proporciona la tensió de sortida més alta, aconseguint així un nivell superior d’optimització de la potència.

Hi ha diverses marques diferents d’IC comercials (principalment microcontroladors) que, en principi, poden implementar un seguidor de màxima tensió. No obstant això, requereixen programació i són menys rendibles que una solució de senyal mixt. Complementar un disseny de Dialog GreenPAK ™ pot afectar positivament la assequibilitat, la mida i la modularitat del disseny. Aquest disseny aprofita els avantatges d’integrar tant circuits analògics com digitals en un sol xip.

En aquesta instrucció, s’implementa la interfície analògica i la lògica digital necessàries per implementar un cercador de tensió màxima (o eventualment mínima) entre vuit fonts diferents.

Per implementar el monitor de tensió analògica màx / min de 8 canals s’utilitza un SLG46620G.

A continuació, es descriuen els passos necessaris per entendre com s'ha programat la solució per crear el monitor analògic de voltatge màx / min de 8 canals. Tot i això, si només voleu obtenir el resultat de la programació, descarregueu-vos el programari GreenPAK per veure el fitxer de disseny GreenPAK ja completat. Connecteu el kit de desenvolupament GreenPAK a l'ordinador i premeu el programa per crear el monitor de tensió analògica de màx / min de 8 canals.

Pas 1: diagrama de blocs

La figura 1 mostra el diagrama global del sistema implementat.

Una cadena de fins a 8 fonts de voltatge variable es multiplexa i s’interfaccia al mòdul ADC d’un GreenPAK connectat a un disseny intern personalitzat capaç de seleccionar la font amb el voltatge més alt respecte a les altres. La lògica interna emet aquesta informació per mostrar-la o processar-la posteriorment.

El disseny es basa en el producte GreenPAK SLG46620G, perquè incorpora tots els blocs de construcció analògics i digitals necessaris per a l’aplicació. En aquesta implementació, la matriu s’escaneja mitjançant un multiplexor analògic ADG508 directament impulsat pel GreenPAK IC.

La informació de sortida és un número digital de 3 bits corresponent al nombre de font de tensió a la tensió màxima. Una manera directa d’obtenir aquesta informació és mostrar el número mitjançant una pantalla de 7 segments. Es pot aconseguir fàcilment mitjançant la interfície de la sortida digital del SLG46620G amb un controlador de pantalla de 7 segments, com la solució GreenPAK descrita a la referència o amb un IC 74LS47 comú.

El circuit presentat busca la màxima tensió. Per convertir el disseny en un cercador de tensió mínima, s’ha d’afegir un circuit de precondicionament simple entre el multiplexor analògic i l’entrada analògica GreenPAK, restant la sortida del multiplexor d’una tensió de referència d’1 V.

Pas 2: Principi de funcionament

El disseny té com a objectiu seleccionar la font amb tensió màxima, per tant es realitza un escaneig a tota la matriu mentre s’emmagatzema l’últim valor màxim i es compara amb el següent valor d’entrada (que pertany a la següent font de tensió de l’exploració).

A continuació, ens referirem a una seqüència de multiplexació completa al llarg de totes les entrades com a "escaneig" o "bucle".

La comparació entre dos valors no s’aconsegueix mitjançant components ACMP (tanmateix, disponibles al SLG46620G), sinó més aviat mitjançant el mòdul DCMP, una vegada que els valors són digitalitzats respectivament. Es tracta d’una tècnica avançada i refinada abordada per primera vegada a Reference.

La figura 2 mostra com s'estructura el SLG46620G per a aquest disseny.

El senyal d’entrada analògica passa a l’entrada ADC a través del component PGA amb un guany establert de 1. També hi ha diverses opcions de guany per trobar la millor coincidència amb l’electrònica de condicionament frontal dedicada a assignar les tensions d’entrada a 0-1 V del mòdul GreenPAK ADC.

L'ADC funciona en mode de punt final i converteix el senyal analògic en un codi digital de 8 bits, que després es transfereix al mòdul DCMP. El codi digital també s’introdueix al bloc SPI, configurat com a buffer ADC / FSM, on es pot emmagatzemar un codi digital i no canviarà fins que arribi el següent pols a l’entrada SPI CLK. Fixeu-vos que un bloc lògic dedicat condueix l'entrada SPI CLK. Investigarem aquesta part més endavant, ja que aquesta és la lògica "bàsica" responsable d'un correcte funcionament. Un nou codi digital s’emmagatzema al mòdul SPI només si pertany al voltatge màxim d’entrada real.

El component DCMP s’utilitza per comparar les dades ADC actuals amb l’últim guanyador (que és l’últim màxim trobat) que s’emmagatzema al bloc SPI. Generarà un pols a la sortida OUT + quan les noves dades ADC siguin superiors a les anteriors. Utilitzem el senyal OUT + per actualitzar el bloc SPI amb el nou guanyador.

Un senyal de rellotge global genera conversions ADC i horaris generals. Un cop realitzada una conversió, els senyals de sortida INT de l’ADC impulsen, coordinats en el temps amb la sortida de dades paral·leles ADC. Utilitzem la sortida INT també per incrementar un comptador binari de 3 bits, implementat per DFF a Matrix1, que és útil per tres motius:

1. Les línies de sortida del comptador s’adrecen al multiplexor analògic extern, servint així la següent tensió d’entrada a l’ADC;

2. El recompte es congela en un registre de 3 bits (implementat a Matrix1) per emmagatzemar el guanyador temporal durant un escaneig;

3. El recompte es descodifica per actualitzar un segon registre de 3 bits (implementat a Matrix0) un cop finalitzada la digitalització.

Pas 3: Implementació de la lògica

El mòdul ADC proporciona seqüencialment les dades convertides de totes les tensions d’entrada, una darrere l’altra, de manera indefinida. Una vegada que el multiplexor s'adreça a 0b111 (decimal 7), el comptador es desplaça a 0b000 (decimal 0), començant així una nova exploració de les tensions d'entrada.

Durant l'escaneig, el senyal de sortida ADC INT es genera quan la sortida de dades paral·leles és vàlida. Quan aquest senyal polsa, el multiplexor analògic ha de canviar a la següent entrada, proporcionant a la PGA la tensió corresponent. Per tant, la sortida ADC INT és el senyal de rellotge directe del comptador binari de 3 bits de la figura 2, la paraula de sortida paral·lela de 3 bits de la qual dirigeix directament el multiplexor analògic extern ("selecció V" a la figura 1).

Vegem ara un exemple on se suposa que les tensions d'entrada tenen les relacions següents:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

La figura 3 representa els principals senyals implicats en el mecanisme de decisió màxima.

Atès que les dades es clouen al registre de memòria intermèdia SPI de manera sincronitzada amb els impulsos INT, existeix una finestra de comparació on es compara el contingut de la memòria intermèdia SPI amb el següent resultat de conversió ADC. Aquest temps particular resulta en la generació d’impulsos OUT + a la sortida DCMP. Podem aprofitar aquests impulsos per carregar nous valors al registre de memòria intermèdia SPI.

Com es desprèn de la línia de dades de memòria intermèdia SPI de la figura anterior, el registre SPI sempre conté, temps per temps, el valor més gran entre les 8 entrades i només s’actualitza quan el mòdul DCMP detecta un valor més gran (referint-se al DCMP OUT + línia de sortida de la trama, els polsos que falten fan que V2 romangui bloquejat al registre fins que no es compari amb V5).

Pas 4: resoldre el punt mort

Si la lògica implementada seria tal i com s’ha descrit anteriorment, és clar que ens trobaríem amb una situació de bloqueig: el sistema només és capaç de detectar tensions superiors a la corresponent al que s’emmagatzema al registre de memòria intermèdia SPI.

Això també és vàlid en cas que aquesta tensió disminueixi i després una altra entrada, fins ara inferior a aquesta, es converteixi en la més alta: mai no es detectaria. Aquesta situació s’explica millor a la figura 4, on només hi ha 3 voltatges d’entrada pel bé de claredat.

En el moment de la iteració 2, V3 cau i V1 és el voltatge màxim real. Però el mòdul DCMP no proporciona cap impuls perquè les dades emmagatzemades al registre de memòria intermèdia SPI (corresponent a 0,6 V) són més grans que les corresponents a V1 (0,4 V).

Aleshores, el sistema es comporta com un cercador màxim “absolut” i no actualitza la sortida correctament.

Una bona manera de superar aquest problema és forçar la recàrrega de les dades al registre de memòria intermèdia SPI quan el sistema completi un cicle de sondeig complet de tots els canals.

De fet, si el voltatge d’aquesta entrada segueix sent el més alt, res no canvia i el control continua amb seguretat (fent referència a la figura 4 anterior, aquest és el cas de les iteracions de bucle 0 i 1). D’altra banda, si la tensió d’aquesta entrada per casualitat baixa a un valor inferior a una altra entrada, la recàrrega del valor dóna la possibilitat al mòdul DCMP de produir un impuls OUT + en comparar-lo amb el nou valor màxim (aquest és el cas de les iteracions de bucle 2 i 3).

Per superar el problema és necessari un circuit lògic. Ha de generar un senyal de rellotge al component SPI quan el bucle aconsegueix l’entrada màxima real, forçant així una recàrrega de la seva paraula de dades actualitzada al registre de memòria intermèdia SPI. Això es discutirà a les seccions 7.2 i 7.6 següents.

Pas 5: Configuració del dispositiu: circuit Matrix0

El SLG46620G té dos blocs Matrix, tal com es mostra a la figura 2. Les figures següents mostren les configuracions de dispositiu respectives.

La part superior del circuit és el "Loop Register" realitzat amb 3 DFF (DFF0, DFF1 i DFF2). Es refresca després de cada bucle del multiplexor d'entrada per enviar a un controlador de visualització de 7 segments el número binari del "guanyador", que és l'entrada amb el voltatge més alt en l'últim escaneig. Tant el rellotge dels DFF com les dades provenen de la lògica implementada a Matrix1 mitjançant, respectivament, els ports P12, P13, P14 i P15.

La part inferior és la part frontal analògica amb entrada al pin 8 i PGA amb guany x1. La sortida ADC INT va tant a la lògica de rellotge de SPI com a Matrix1 mitjançant el port P0, on servirà com a senyal de rellotge per al comptador implementat.

Les sortides de dades paral·leles ADC i SPI s’etiqueten respectivament amb NET11 i NET15 per connectar-se al component DCMP de Matrix1.

Pas 6: Configuració del dispositiu: lògica de rellotge SPI

Com s'ha assenyalat anteriorment a la secció "Implementació lògica", el registre de memòria intermèdia SPI s'actualitza cada vegada que una comparació entre el valor emmagatzemat real i les noves dades de conversió ADC genera un impuls a la sortida DCMP OUT +.

La integritat del senyal s’assegura si aquest senyal és AND-ed amb la sortida ADC INT. D’aquesta manera, s’eviten espigues i falsos desencadenaments.

També hem subratllat que per ometre situacions de bloqueig, el buffer SPI s’ha d’actualitzar quan el bucle arriba a les dades reals del guanyador.

Aleshores, hi ha tres senyals en joc per obtenir un SPI correcte:

1. Sortida ADC INT (LUT0-IN1)

2. Sortida DCMP OUT + (LUT0-IN0 mitjançant el port P10)

3. El recompte és igual al senyal de tancament (LUT0-IN2 a través del port P11)

Els dos primers són AND-ed i ambdós OR-ed amb aquest últim a LUT0, la implementació de la qual es configura com a la figura 6.

Pas 7: Configuració del dispositiu: propietats dels components de Matrix0

Les figures 7-10 mostren la resta de finestres de propietats dels components que pertanyen a Matrix0.

Pas 8: Configuració del dispositiu: circuit Matrix1

Pas 9: Configuració del dispositiu: comptador binari de 3 bits

La part superior del circuit conté elements lògics, principalment un comptador binari de 3 bits marcat per la sortida ADC INT, com ja s’ha comentat. Aquest comptador s’implementa amb un esquema força “estàndard” que es mostra a la Figura 12.

Aquest comptador es realitza en el nostre disseny mitjançant xancles DFF9, DFF10, DFF11 i INV1, LUT4, LUT8. La sortida DFF9 és el LSB, mentre que DFF11 és el MSB, tal com es mostra a la figura 13.

LUT4 es configura com a XOR mentre LUT8 realitza la lògica AND-XOR de la figura 12.

Les sortides de comptador van a tres pins de sortida digitals per dirigir-se al multiplexor analògic extern.

LUT10 descodifica el codi del comptador quan es completa l’escaneig i alimenta un impuls a Matrix0 mitjançant DLY8 i el port P12. Això simplement s’aconsegueix amb la sortida AND del comptador, descodificant així el número 7 dec (binari 0b111, final de bucle).

Pas 10: Configuració del dispositiu: lògica de comparació de 3 bits

La figura 15 mostra el circuit utilitzat per detectar quan el bucle itera a l’adreça actual del "guanyador". En aquest cas, com ja s'ha comentat, un pols digital hauria de forçar una recàrrega del resultat actual de l'ADC per resoldre una possible situació de bloqueig.

L'adreça "guanyadora" s'emmagatzema al registre temporal de Matrix1 (vegeu més avall), mentre que l'adreça actual és emesa pel comptador binari.

Les portes XNOR proporcionen una sortida veritable (lògica 1 o "alta") quan les dues entrades són iguals. AND-ing aquest senyal per a tots els bits (LUT9) ens dóna un pols quan els dos codis binaris són iguals. Podeu trobar detalls sobre les portes XOR com a verificador de paritat a Referència.

El senyal ‘Counter-equals-Latch’ es passa a Matrix0 mitjançant el port P11.

Pas 11: Configuració del dispositiu: lògica de comparació digital i registre temporal

La part inferior de la figura 11 (ressaltada a la figura 16) mostra el bloc DCMP, la part de presa de decisions d’aquest disseny.

DFF6, 7 i 8 formen un registre de 3 bits per emmagatzemar el número d’entrada temporal “guanyador” mentre s’executa el bucle. Les entrades als xancles són les sortides de comptador binari de 3 bits, tal com són visibles al circuit global Matrix1 de la Figura 11, que aquí es salta per motius de claredat.

Les sortides d’aquest registre no poden conduir directament la pantalla de 7 segments perquè el valor emmagatzemat aquí canvia durant un escaneig i només s’ha de considerar ‘vàlid’ al final de l’escaneig.

Per aquest motiu, les sortides de registre temporals es connecten al registre de bucles de Matrix0 mitjançant els ports entre matrius P13, P14 i P15.

És important observar a la figura 16 que el registre temporal és cronometrat per la sortida DCMP OUT + quan l'ADC-SPI registra la comparació com a resultat d'un nou màxim trobat.

El mateix senyal OUT + es passa a Matrix0, SPI CLK Logic, a través del port P10.

Pas 12: Configuració del dispositiu: propietats dels components de Matrix1

Les figures 17-19 mostren les finestres de propietats dels components que pertanyen a Matrix1.

Pas 13: Resultats

Per provar la implementació, s’ha construït un prototip de placa d’avaluació, on les 8 tensions d’entrada analògica s’obtenen mitjançant una sèrie de divisors de resistències amb TrimPots (com es mostra a la figura 20).

El multiplexor utilitzat és un ADG508, una peça que pot funcionar amb alimentació única (12 V).

El controlador de pantalla de 7 segments és un 74LS47. Descodifica una paraula d’entrada paral·lela i condueix directament una pantalla de 7 segments d’ànode comú.

La placa d’avaluació té un connector d’angle dret de 2x10 per connectar-lo directament a una plataforma de desenvolupament avançat GreenPAK al seu connector d’expansió, tal com es mostra a la figura 21.

La conjunció amb la plataforma de desenvolupament avançat GreenPAK fa que sigui molt senzill mesurar els senyals per fer una comprovació ràpida. Per exemple, la figura 22 mostra un conjunt de senyals (respectivament CLOCK, sortida ADC INT i sortida DCMP OUT +) capturats per un analitzador lògic HP 54620A. Les formes d’ona són activades per una vora ascendent del senyal OUT + (a l’abast etiquetat com a "A> B"), per tant, es tracta d’una captura de forma d’ona quan es detecta una nova tensió màxima entre les entrades analògiques. De fet, es va obtenir girant un dels TrimPots del tauler d’avaluació per augmentar el voltatge corresponent que es mostra a la figura 22.

La figura 23 mostra l’esquema del tauler d’avaluació.

Conclusió

En aquesta instrucció, hem implementat un cercador de tensió màxima (o mínima) de vuit canals per utilitzar-lo com a addició habitual als sistemes de control multicanal. L'enfocament presentat explota les funcions avançades dels components de GreenPAK i mostra com és possible integrar-se en un sol xip amb funcions analògiques i digitals. Es poden substituir diversos IC comercials per Dialog GreenPAK, de manera que es poden reduir la mida i el cost de l’aplicació.

Recomanat:

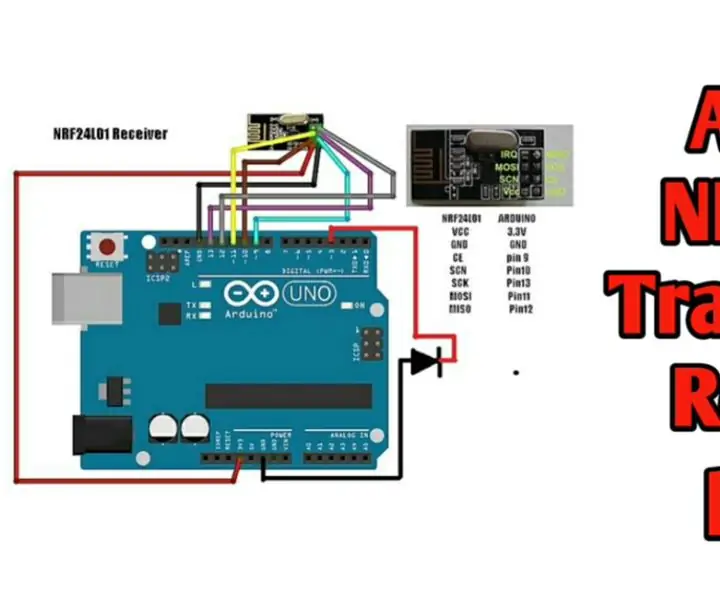

Comandament a distància sense fils que utilitza el mòdul NRF24L01 de 2,4 Ghz amb Arduino - Nrf24l01 Receptor transmissor de 4 canals / 6 canals per quadcòpter - Helicòpter Rc - Avi

Comandament sense fils que utilitza un mòdul NRF24L01 de 2,4 Ghz amb Arduino | Nrf24l01 Receptor transmissor de 4 canals / 6 canals per quadcòpter | Helicòpter Rc | Avió Rc amb Arduino: per fer funcionar un cotxe Rc | Quadcopter | Drone | Avió RC | Vaixell RC, sempre necessitem un receptor i un transmissor, suposem que per RC QUADCOPTER necessitem un transmissor i un receptor de 6 canals i aquest tipus de TX i RX és massa costós, així que en farem un al nostre

Antena interior BIQUAD, feta de coure i fusta per a la recepció de canals HDTV a la banda UHF (CANALS 14-51): 7 passos

Antena interior BIQUAD, feta de coure i fusta per a la recepció de canals HDTV a la banda UHF (CANALS 14-51): Al mercat hi ha una gran varietat d’antenes per a televisió. Els més populars segons els meus criteris són: UDA-YAGIS, Dipol, Dipol amb reflectors, Patch i antenes logarítmiques. Depenent de les condicions, la distància des del transmissor a

Detector de voltatge sense contacte de bricolatge: 4 passos (amb imatges)

Detector de tensió sense contacte de bricolatge: tothom es cansa d’utilitzar aquests cables que pengen al multímetre per detectar que qualsevol voltatge sigui un cable o un circuit, però hi ha una manera de fer-ho mitjançant un detector de tensió sense contacte. Sí, això sona net i senzill. Per tant, fem-ho amb només 4 Components

Amplificador analògic de 8 canals per a PC o HomeTheater: 12 passos (amb imatges)

Amplificador analògic de 8 canals per a PC o HomeTheater: aquest és el meu primer instructable. T’ensenyaré a fer un amplificador de 8 canals per a un ordinador o sistema d’àudio amb sortides analògiques separades, l’he utilitzat per al meu ordinador de sobretaula, per veure pel·lícules, escoltar música en HD i jugar a jocs, a més

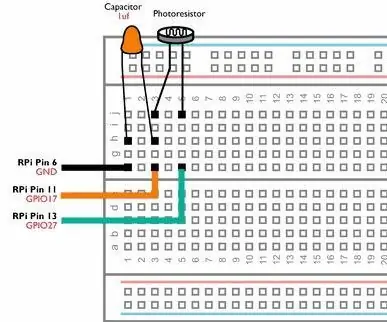

Circuits GPIO de Raspberry Pi: utilitzar un sensor analògic LDR sense ADC (convertidor analògic a digital): 4 passos

Circuits GPIO de Raspberry Pi: utilitzant un sensor analògic LDR sense ADC (convertidor analògic a digital): a les instruccions anteriors us hem mostrat com podeu enllaçar els pins GPIO de Raspberry Pi amb LEDs i commutadors i com els pins GPIO poden ser alts. o Baixa. Però, i si voleu utilitzar el vostre Raspberry Pi amb un sensor analògic? Si volem utilitzar un