Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:12.

- Última modificació 2025-01-23 14:37.

En aquest manual es descriurà com implementar un convertidor analògic a digital de 8 bits (ADC) al SLG46855V que pugui detectar el corrent de càrrega i la interfície amb una MCU mitjançant I2C. Aquest disseny es pot utilitzar per a diverses aplicacions de detecció de corrent, com ara amperímetres, sistemes de detecció d’errors i indicadors de combustible.

A continuació es descriuen els passos necessaris per entendre com s'ha programat la solució per crear el sentit actual de l'ADC. Tot i això, si només voleu obtenir el resultat de la programació, descarregueu-vos el programari GreenPAK per veure el fitxer de disseny GreenPAK ja completat. Connecteu el kit de desenvolupament GreenPAK a l'ordinador i premeu el programa per crear el sentit actual de l'ADC.

Pas 1: Arquitectura ADC

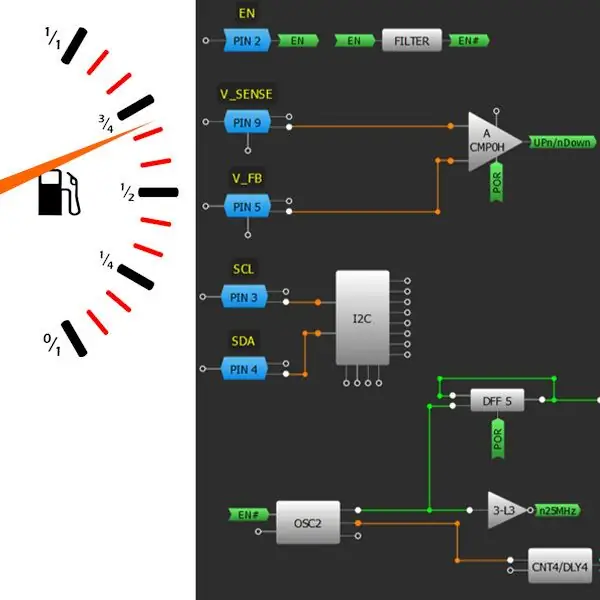

L’ADC es compon essencialment d’un comparador analògic i d’un convertidor digital a analògic (DAC). El comparador detecta la tensió d’entrada enfront del voltatge de sortida del DAC i, posteriorment, controla si s’ha d’incrementar o disminuir el codi d’entrada del DAC, de manera que la sortida del DAC convergisca a la tensió d’entrada. El codi d’entrada DAC resultant es converteix en el codi de sortida digital ADC.

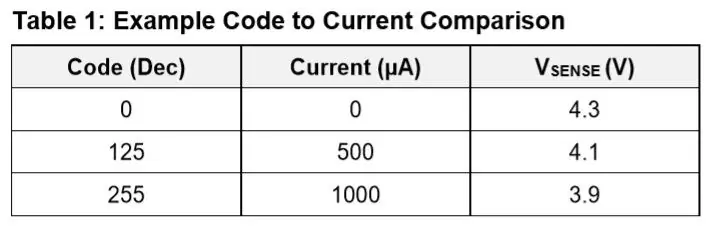

En la nostra implementació, creem un DAC mitjançant una xarxa de resistències controlada per modulació d’amplitud d’impulsos (PWM). Podem crear fàcilment una sortida PWM precisa controlada digitalment mitjançant GreenPAK. Quan es filtra el PWM es converteix en el nostre voltatge analògic i, per tant, serveix com un DAC eficaç. Un avantatge clar d’aquest enfocament és que és fàcil establir les tensions que corresponen a codi zero i escala completa (compensació i guany equivalents) simplement ajustant els valors de la resistència. Per exemple, un usuari vol llegir idealment el codi zero d’un sensor de temperatura sense corrent (0 µA) que correspon a 4,3 V i el codi a escala completa a 1000 µA que correspon a 3,9 V (taula 1). Això s’implementa fàcilment simplement establint uns quants valors de resistència. Si el rang d’ADC coincideix amb l’interval del sensor d’interès, aprofitem al màxim la resolució ADC.

Una consideració de disseny per a aquesta arquitectura és que una freqüència PWM interna ha de ser molt més ràpida que la velocitat d’actualització de l’ADC per evitar un comportament insuficient del seu bucle de control. Com a mínim, hauria de ser més llarg que el comptador de dades ADC dividit per 256. En aquest disseny, el període d'actualització de l'ADC s'estableix a 1,3312 ms.

Pas 2: Circuit intern

L’ADC flexible es basa en el disseny presentat a Dialog Semiconductor AN-1177. La velocitat del rellotge augmenta d’1 MHz a 12,5 MHz per tal de marcar el comptador ADC, ja que el SLG46855 té un rellotge de 25 MHz disponible. Això permet una taxa d’actualització molt més ràpida per a una resolució de mostra més fina. El LUT que marca el rellotge de dades ADC es canvia, de manera que passarà pel senyal de 12,5 MHz quan el PWM DFF sigui baix.

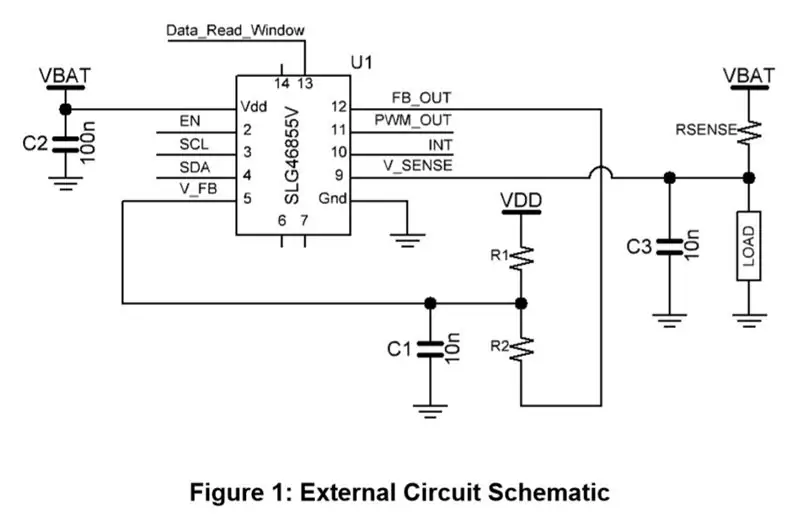

Pas 3: Circuit extern

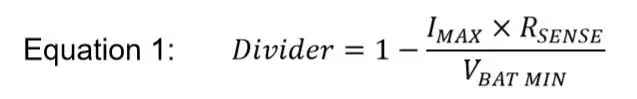

S’utilitza una resistència externa i una xarxa de condensadors per convertir un PWM en una tensió analògica tal com es mostra a l’esquema del circuit de la Figura 1. Els valors es calculen per a la resolució màxima del màxim corrent que detectarà el dispositiu. Per aconseguir aquesta flexibilitat, afegim resistències R1 i R2 en paral·lel a VDD i terra. Un divisor de resistències divideix VBAT al costat baix del rang de tensió. La relació divisora per a un VBAT mínim esperat es pot resoldre mitjançant l’equació 1.

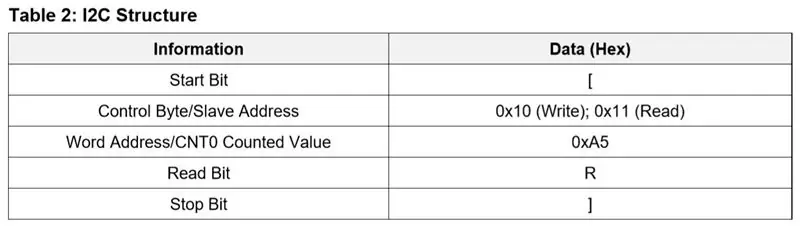

Pas 4: Llegiu les instruccions I2C

La taula 1 descriu l'estructura d'ordres I2C per llegir les dades emmagatzemades a CNT0. Les ordres I2C requereixen un bit d’inici, un byte de control, una adreça de paraula, un bit de lectura i un bit d’aturada.

A continuació s’escriu un exemple d’ordre I2C per llegir de nou el valor comptat CNT0:

[0x10 0xA5] [0x11 R]

El valor comptat que es llegeix serà el valor del codi ADC. Com a exemple, s'inclou un codi Arduino al fitxer ZIP d'aquesta nota d'aplicació al lloc web de Dialog.

Pas 5: Resultats

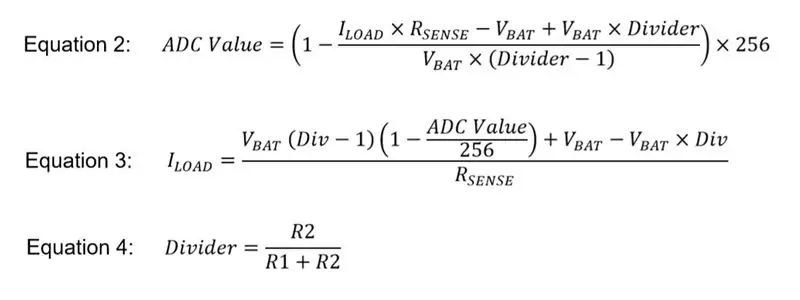

Per provar la precisió del disseny de sentit del corrent ADC, es van comparar els valors mesurats a un corrent de càrrega i un nivell de VDD determinats amb un valor teòric. Els valors teòrics de l'ADC es van calcular amb l'equació 2.

La ILOAD que es correlaciona amb un valor ADC es troba amb l'equació 3.

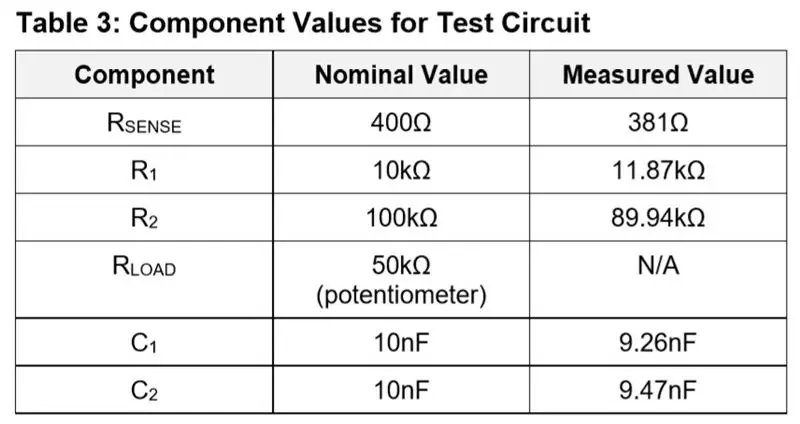

Per als resultats següents, he utilitzat aquests valors de components que es mostren a la taula 3.

La resolució del valor ADC a conversió ILOAD es pot calcular utilitzant l’equació 3 amb els valors mesurats a la taula 2 i el valor ADC establert a 1. Amb un VBAT de 3,9 V, la resolució és de 4,96 µA / div.

Per tal d’optimitzar el circuit de detecció de corrent ADC a un nivell VDD mínim de 3,6 V amb un corrent màxim de 1100 µA i una resistència de detecció de 381 Ω, el coeficient divisor ideal seria de 0,884, basat en l’equació 1. Amb els valors donats a la taula 2, el divisor real té un coeficient divisor de 0,876. Com que és una mica menor, permetrà un rang de corrent de càrrega una mica més gran, de manera que els valors ADC són propers a l'interval complet però no es desbordaran. El valor divisor real es calcula amb l’equació 4.

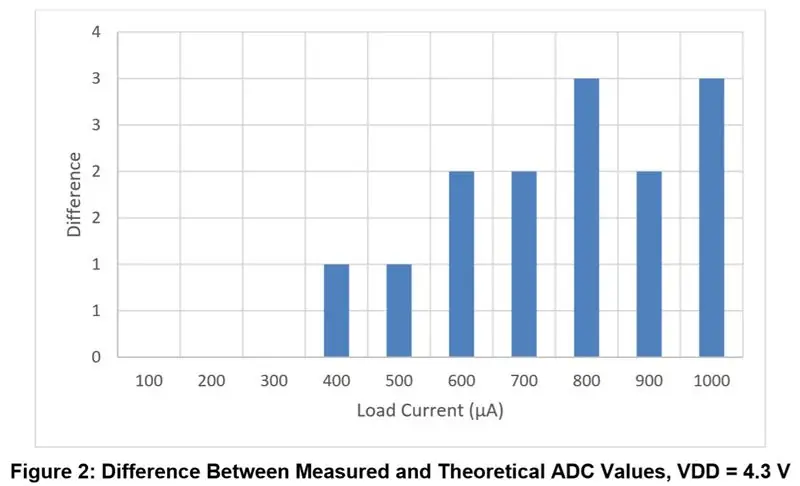

A la part superior (figures 2-6, taules 4-6) es mostren les mesures del circuit a tres nivells de tensió: 4,3 V, 3,9 V i 3,6 V. Cada nivell mostra un gràfic que mostra la diferència entre els valors mesurats i teòrics de l’ADC. Els valors teòrics s’arrodoneixen al enter sencer més proper. Hi ha un gràfic resum per comparar les diferències en els tres nivells de tensió. Després hi ha un gràfic que mostra la correlació entre els valors ADC teòrics i el corrent de càrrega als diferents nivells de tensió.

Conclusió

El dispositiu es va provar a tres nivells de voltatge: 3,6 V, 3,9 V i 4,3 V. El rang d’aquestes tensions modela una bateria de ions de liti completa que es descarrega al seu nivell nominal. Dels tres nivells de tensió, s’observa que el dispositiu normalment era més precís a 3,9 V per al circuit extern escollit. La diferència entre els valors mesurats i teòrics de l'ADC era només 1 valor decimal desactivat a corrents de càrrega de 700 - 1000 µA. En el rang de tensió donat, els valors ADC mesurats van ser 3 punts decimals per sobre de les condicions nominals en el pitjor dels casos. Es poden fer més ajustos al divisor de resistències per optimitzar diferents nivells de voltatge VDD.

Recomanat:

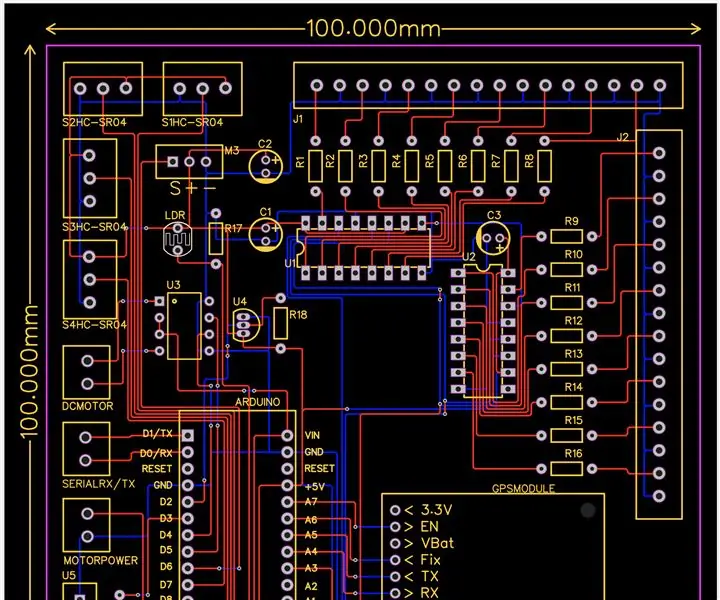

Rover-One: donar un cervell a un camió o cotxe RC: 11 passos

Rover-One: donar un cervell a un camió / cotxe RC: aquest instructiu es troba en un PCB que he dissenyat anomenat Rover-One. Rover-One és una solució que he dissenyat per agafar un cotxe / camió RC de joguina i donar-li un cervell que inclogui components per detectar el seu entorn. Rover-One és un PCB de 100 mm x 100 mm dissenyat en EasyED

Donar a Thomas el tren la capacitat de conduir de nit: 5 passos

Donar a Thomas el tren la capacitat de conduir a la nit: aquest instructiu us ensenyarà a crear un sistema de llums per advertir els passatgers que s’esperen quan s’acosta un tren i també com fer que aparegui un missatge a un ordinador portàtil quan el tren es troba a la estació. Un so per a quan el tren passa l’estat

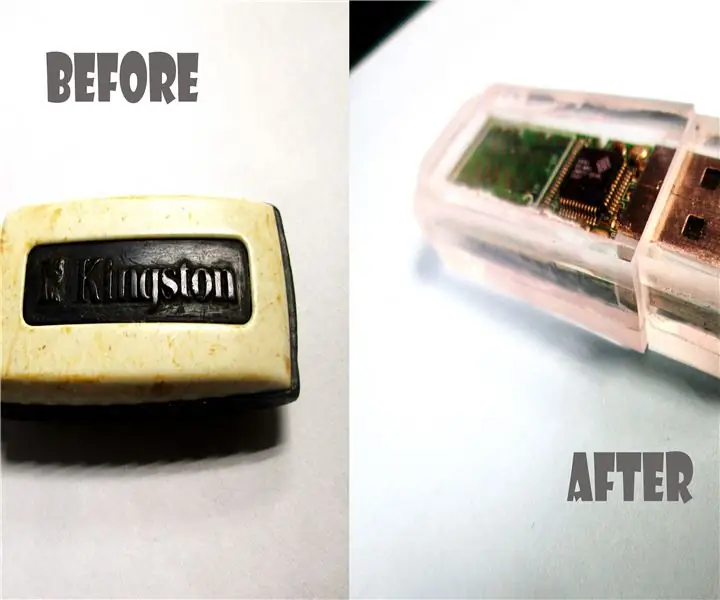

Donar al meu USB una nova vida: 7 passos

Donar una vida nova al meu USB: Tinc aquest USB Kingston (o unitat flash si voleu) que vaig comprar fa diversos anys. Els anys de servei van demostrar la seva aparició ara. La tapa ja ha desaparegut i la carcassa sembla treta d’un pati d’escombraries amb traces de decoloració. La placa USB

El MAC negre o donar vida nova a un cas antic: 9 passos (amb imatges)

El Black MAC o Donar nova vida a un cas vell. Fa un parell de mesos vaig rebre un cas MAC antic. Buit, només quedava un xassís rovellat a l’interior. L’he guardat al taller i la setmana passada em ve al cap. El cas era lleig, cobert de nicotina i brutícia amb moltes ratllades. Primer acostament

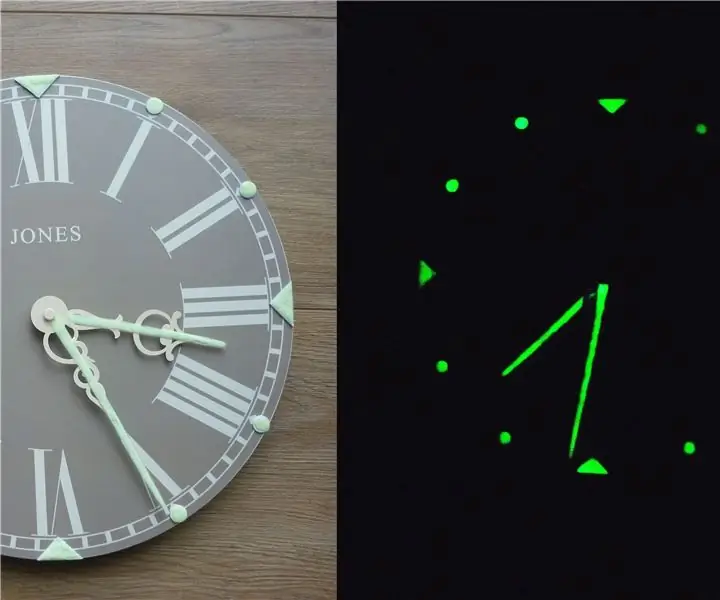

Com donar a un rellotge de paret llums lluminoses i marcadors d'interval de temps: 14 passos (amb imatges)

Com donar a un rellotge de paret agulles lluminoses i marcadors d’interval de temps: volíem un rellotge de paret del dormitori amb agulles lluminoses i una visualització d’intervals de cinc minuts i quart d’hora. Havia de ser llegible sense esforç des del llit i la lluminositat havia de perdurar tota la nit. La pintura lluminosa que s’utilitza als rellotges moderns tendeix