Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:12.

- Última modificació 2025-01-23 14:37.

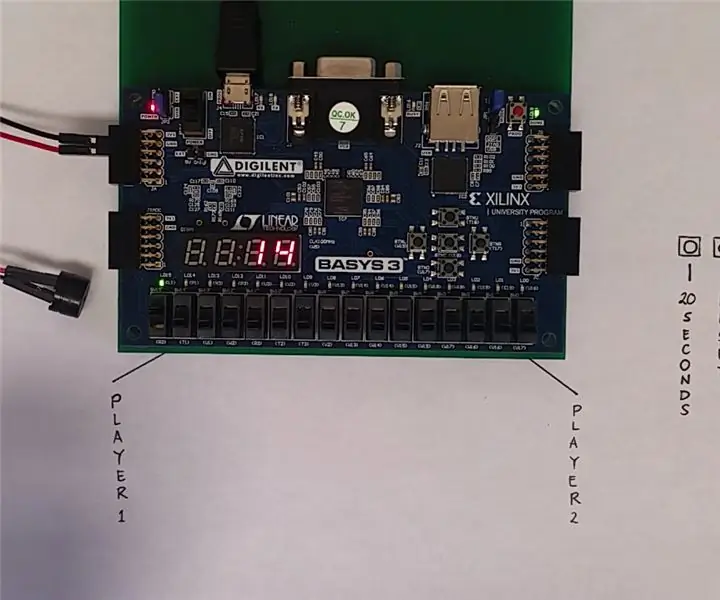

El sistema de brunzidors competitius dissenyat en aquest projecte funciona de manera similar als sistemes de brunzidors utilitzats a les competicions regionals i nacionals de ciències. Aquest projecte es va inspirar en la meva participació durant tres anys amb l’equip de ciències de la meva escola secundària. Sempre hem tingut el desig de recrear el sistema de timbre de bloqueig amb un temporitzador de 5 i 20 segons.

Per proporcionar una mica d’antecedents sobre el sistema de brunzidors, els brunzidors de ciència ciència estan programats per introduir un màxim de 8 jugadors (amb 8 brunzidors separats). Un cop premut un zumbador, s'encendrà el zumbador de la primera persona per indicar quin jugador rep la pregunta. La resta de jugadors estaran "bloquejats", cosa que significa que els seus brunzidors no respondran fins que el moderador no restableixi el sistema de brunzidors.

Després que el moderador llegeixi les preguntes, premrà un botó per iniciar el temporitzador de compte enrere que es mostrarà a la pantalla de set segments. Després d'una pregunta de "llançament", el moderador pot prémer el botó dret per iniciar el compte enrere a partir de 5 segons. Mentrestant, després d’una pregunta “addicional”, el moderador pot prémer el botó esquerre per iniciar el compte enrere a partir dels 20 segons. Un cop el temporitzador arriba a zero, un timbre de so indicarà que el jugador s'ha quedat sense temps.

Per restablir el sistema i el temporitzador de compte enrere, el moderador pot prémer el botó central. Per restablir el mecanisme de bloqueig i els LED del reproductor, els commutadors del jugador 1 i del jugador 2 han d’estar apagats.

Pas 1: materials

Necessitareu el següent:

- Tauler Basys3 (o tauler FPGA equivalent)

- Cable USB Micro-B

- Altaveu (he utilitzat un altaveu passiu)

- 2 cables

- Programari per implementar al FPGA (he utilitzat Vivado)

- Fitxer Competitive Buzzer System

Pas 2: diagrama de la caixa negra

El diagrama del quadre negre mostra les entrades i sortides que s’utilitzaran en aquest sistema de brunzidors.

ENTRADES:

player1, player2 Aquestes entrades estan connectades a dos commutadors de la placa Basys3. Per comoditat, s’utilitzaran els commutadors més a l’esquerra i a la dreta.

reset El botó central s'utilitzarà per representar el botó de reset.

count_down_20_sec El botó esquerre s'utilitzarà per representar el botó del temporitzador de 20 segons.

count_down_5_sec El botó dret s'utilitzarà per representar el botó del temporitzador de 20 segons. Per assegurar-vos que s'iniciï el temporitzador de 20 i 5 segons, manteniu premut el botó fins que la pantalla de set segments mostri el temporitzador.

CLK La placa FPGA generarà un rellotge que funciona amb una freqüència de 10 ns.

SORTIDES:

altaveu La sortida dels altaveus està connectada a un brunzidor o altaveu extern. Haureu de connectar l’altaveu als ports pmod JA de la placa Basys3. Aquest pas es descriurà a continuació.

speaker_LED Aquesta sortida està connectada a un LED al centre de la placa i només indicarà quan la sortida d’altaveu del FPGA és alta. Podeu utilitzar-ho per provar el vostre altaveu extern. Tingueu en compte que és possible que alguns dels ports pmod no funcionin bé, de manera que podeu provar-ne de diferents i utilitzar el LED per comprovar si l’altaveu hauria d’estar encès.

SEGMENTS Aquesta sortida està connectada als vuit segments individuals de la pantalla de set segments, inclòs el punt decimal.

DISP_EN Aquesta sortida està connectada als quatre ànodes de la pantalla de set segments.

player_LED Aquesta sortida és un senyal de 2 paquets que està connectat als LED situats per sobre dels commutadors player1 i player2. El LED indica el primer jugador que gira el seu commutador corresponent. Tingueu en compte que els dos LED no es poden encendre simultàniament.

Pas 3: connectar l’altaveu extern

Per connectar l’altaveu extern a la placa Basys3, agafeu els dos cables i connecteu-los tal com s’indica a la imatge anterior. La línia blanca connecta el terminal negatiu de l’altaveu al port de terra de la placa. La línia vermella connecta el terminal positiu de l’altaveu al port JA10 pmod de la placa.

El fitxer de restriccions està dissenyat perquè qualsevol port de JA1 a JA10 funcioni. Tanmateix, alguns pins del tauler no responen, de manera que si JA10 no funciona, podeu provar els altres ports.

Pas 4: diagrama estructural

La imatge superior mostra el diagrama estructural del sistema de brunzidors competitius que inclou tots els components que formen el mòdul principal. Les seves descripcions són les següents:

player_lockout_LED1 El component LED de bloqueig del reproductor és una màquina d’estats finits que utilitza una codificació en calent. Té quatre entrades: player1, player2, reset i CLK. Conté una sortida de paquet de 2 bits player_LED. Les entrades i sortides del component player_lockout_LED1 estan connectades directament a les entrades i sortides amb el mateix nom del mòdul principal.

buzzer_tone1 El component de buzzer es basa en aquest codi publicat en un fòrum

stackoverflow.com/questions/22767256/vhdl-… No obstant això, es va modificar per emetre un so continu amb una freqüència de 440 Hz (nota A). L'entrada d'habilitació està connectada a un senyal buzzer_enable que és una sortida del component down_counter_FSM1.

clk_div1 El component divisor de rellotge és una versió modificada del divisor de rellotge del professor Bryan Mealy proporcionat a PolyLearn. Alenteix el rellotge, de manera que el període de sortida és d’1 segon.

down_counter_FSM1 El comptador descendent és un FSM dissenyat per comptabilitzar fins a zero. Els dos temps d’inici possibles són 20 o 5, que escull l’entrada de l’usuari. Surt '1' quan el temporitzador ha arribat a zero per indicar que s'ha esgotat el temps. Aquesta sortida actua com a habilitació per al component de to del brunzidor. El comptador també emet un senyal de paquet de 8 bits que envia un BCD de 8 bits que s’envia al descodificador de segments. Una altra sortida és el counter_on, que també està connectat a l'entrada vàlida del descodificador de segments.

sseg_dec1 El component del descodificador de set segments es proporciona a PolyLearn i va ser escrit pel professor Bryan Mealy. Utilitza una entrada BCD proporcionada per down_counter_FSM1 i genera l'equivalent decimal a la pantalla de set segments. Quan el comptador està activat, l’entrada vàlida és alta. Això permet al descodificador mostrar el número decimal a la pantalla de set segments. Quan el comptador està apagat, l’entrada vàlida és baixa. La pantalla de set segments només mostrarà quatre guions.

Pas 5: diagrama de màquina d'estat finit (FSM)

La llista de sensibilitat de la màquina d’estats finits inclou el jugador 1, el jugador 2, el restabliment i el rellotge. La sortida FSM és un reproductor de paquets de 2 bits_LED connectat a dos LEDs de la placa Basys3. La màquina d'estats finits mostra els tres estats següents:

ST0 és l'estat inicial. En aquest estat, els dos LED estan apagats. El FSM es mantindrà en aquest estat si el jugador 1 i el jugador 2 són baixos. Un restabliment asíncron també estableix l'estat a ST0. Quan el commutador del reproductor 1 està configurat a alt, el següent estat serà ST1. Si el commutador player2 està configurat a alt, el següent estat serà ST2.

ST1 és l'estat en què està encès el LED del reproductor 1. El FSM es mantindrà en aquest estat per a qualsevol entrada. Això significa que, fins i tot quan el commutador player2 estigui ajustat immediatament després que el commutador player1 estigui alt, es mantindrà a ST1. Només el restabliment asíncron pot establir el següent estat a ST0.

ST2 és l'estat per al qual està activat el LED player2. Similar a ST !, el FSM es mantindrà en aquest estat per a qualsevol entrada, fins i tot quan el commutador player1 estigui ajustat immediatament després que el commutador player2 estigui alt. Una vegada més, només el restabliment asíncron pot configurar el següent estat a ST0.

Recomanat:

Timbre Arduino: 4 passos

Timbre Arduino: Avui us mostraré com fer un timbre amb un Arduino. Aquest timbre de la porta toca una melodia aleatòria des d’una biblioteca de cançons. Podeu personalitzar el timbre de la porta i afegir encara més cançons. Instal·leu-lo fora del vostre dormitori, aula, oficina o fins i tot vosaltres

Com fer un timbre sense tocar, detecció de temperatura corporal, GY-906, 433 MHz mitjançant Arduino: 3 passos

Com fer un timbre sense tocar, detecció de temperatura corporal, GY-906, 433 MHz utilitzant Arduino: Avui farem un timbre sense tocar, que detectarà la temperatura corporal. En la situació actual, és molt important saber si la temperatura corporal d'algú és superior a la normal, quan algú està tocant. Aquest projecte mostrarà llum vermella si es detecta

Timbre de dos tons mitjançant IC 555: 6 passos

Timbre de dos tons amb IC 555: Vaig veure algú que venia un timbre de dos tons a Aliexpress per 10 dòlars. Immediatament el meu cervell em va dir: estàs seriós? Només invertint una mica del vostre temps i entusiasme, podreu guanyar aquest circuit per menys de 3 dòlars

Converteix el teu timbre amb cable en un timbre intel·ligent amb IFTTT: 8 passos

Convertiu el vostre timbre amb cable en un timbre intel·ligent amb IFTTT: el timbre WiFi converteix el vostre timbre amb cable en un timbre intel·ligent. https://www.fireflyelectronix.com/product/wifidoor

Converteix el teu timbre amb cable en un timbre intel·ligent amb Home Assistant: 6 passos

Converteix el teu timbre amb cable en un timbre intel·ligent amb Home Assistant: converteix el teu timbre amb cable en un timbre intel·ligent. Rebeu una notificació al vostre telèfon o emparelleu-la amb la càmera de la porta principal existent per rebre una alerta de fotos o de vídeo sempre que algú soni al vostre timbre. Més informació a: fireflyelectronix.com/pro