Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:14.

- Última modificació 2025-01-23 14:38.

Analitzaré com compleix el desafiament del disseny de la font d'alimentació de DC-DC Technologies.

Els dissenyadors de sistemes d’energia s’enfronten a una pressió constant del mercat per trobar maneres d’aprofitar al màxim l’energia disponible. En els dispositius portàtils, una major eficiència amplia la durada de la bateria i aporta més funcionalitat als paquets més petits. Als servidors i a les estacions base, els guanys d’eficiència poden estalviar directament la infraestructura (sistemes de refrigeració) i els costos d’explotació (factures d’electricitat). Per satisfer les demandes del mercat, els dissenyadors de sistemes milloren els processos de conversió de potència en diverses àrees, incloses topologies de commutació més eficients, innovacions de paquets i nous dispositius semiconductors basats en carbur de silici (SiC) i nitrur de gal (GaN).

Pas 1: Millora de la topologia del convertidor de commutació

Per aprofitar al màxim la potència disponible, la gent adopta cada vegada més dissenys basats en tecnologia de commutació en lloc de tecnologia lineal. La font d'alimentació de commutació (SMPS) té una potència efectiva superior al 90%. D’aquesta manera, s’allarga la vida de la bateria dels sistemes portàtils, es redueix el cost de l’electricitat per a equips grans i s’estalvia espai utilitzat anteriorment per als components del dissipador de calor.

Canviar a una topologia commutada té certs inconvenients i el seu disseny més complex requereix que els dissenyadors tinguin múltiples habilitats. Els enginyers de disseny han de conèixer les tecnologies analògiques i digitals, l’electromagnètica i el control de bucle tancat. Els dissenyadors de plaques de circuits impresos (PCB) han de prestar més atenció a les interferències electromagnètiques (EMI) perquè les formes d’ona de commutació d’alta freqüència poden causar problemes en circuits analògics i RF sensibles.

Abans de la invenció del transistor, es proposava el concepte bàsic de conversió de potència en mode commutat: per exemple, el sistema de descàrrega inductiva de tipus Kate inventat el 1910, que utilitzava un vibrador mecànic per implementar un convertidor d’impulsió flyback per a un sistema d’encesa automotriu.

La majoria de topologies estàndard existeixen des de fa dècades, però això no vol dir que els enginyers no ajustin els dissenys estàndard per adaptar-se a noves aplicacions, especialment els bucles de control. L'arquitectura estàndard utilitza una freqüència fixa per mantenir una tensió de sortida constant alimentant part del voltatge de sortida (control de mode de tensió) o controlant el corrent induït (control de mode de corrent) en diferents condicions de càrrega. Els dissenyadors milloren constantment per superar els defectes del disseny bàsic.

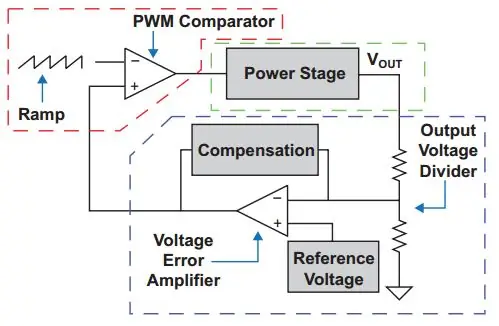

La figura 1 és un diagrama de blocs d’un sistema bàsic de control de mode de voltatge de bucle tancat (VMC). L'etapa de potència consisteix en un interruptor d'alimentació i un filtre de sortida. El bloc de compensació inclou un divisor de tensió de sortida, un amplificador d'error, un voltatge de referència i un component de compensació de bucle. Un modulador d'ample de pols (PWM) utilitza un comparador per comparar el senyal d'error amb un senyal de rampa fixa per produir una seqüència de pols de sortida que és proporcional al senyal d'error.

Tot i que les diferents càrregues del sistema VMC tenen regles de sortida estrictes i són fàcils de sincronitzar amb el rellotge extern, l'arquitectura estàndard té alguns inconvenients. La compensació del bucle redueix l’amplada de banda del bucle de control i alenteix la resposta transitòria; l'amplificador d'errors augmenta el corrent de funcionament i redueix l'eficiència.

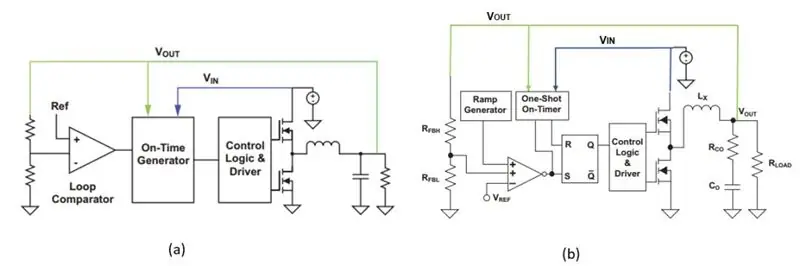

L'esquema de control constant a temps (COT) proporciona un bon rendiment transitori sense compensació de bucle. El control COT utilitza un comparador per comparar la tensió de sortida regulada amb la tensió de referència: quan la tensió de sortida és inferior a la tensió de referència, es genera un impuls fix a temps. Als cicles de treball baixos, això fa que la freqüència de commutació sigui molt alta, de manera que el controlador COT adaptatiu genera un temps d’intervenció que varia amb les tensions d’entrada i sortida, cosa que manté la freqüència gairebé constant a l’estat estacionari. La topologia D-CAP de Texas Instrument és una millora respecte a l’enfocament COT adaptatiu: el controlador D-CAP afegeix un voltatge de rampa a l’entrada del comparador de retroalimentació, que millora el rendiment de la fluctuació reduint la banda de soroll de l’aplicació. La figura 2 és una comparació dels sistemes COT i D-CAP.

Figura 2: Comparació de la topologia COT estàndard (a) i la topologia D-CAP (b) (Font: Texas Instruments) Hi ha diverses variants diferents de la topologia D-CAP per a diferents necessitats. Per exemple, el controlador PWM de mig pont TPS53632 utilitza l’arquitectura D-CAP +, que s’utilitza principalment en aplicacions d’alta intensitat i que pot generar nivells de potència de fins a 1 MHz en convertidors POL de 48 V a 1 V amb una eficiència de fins al 92%.

A diferència de D-CAP, el bucle de retroalimentació D-CAP + afegeix un component que és proporcional al corrent induït per a un control precís de la caiguda. L'amplificador d'error augmentat millora la precisió de la càrrega de CC en diverses condicions de càrrega i línia.

El voltatge de sortida del controlador el defineix el DAC intern. Aquest cicle comença quan la retroalimentació actual arriba al nivell de voltatge d'error. Aquest voltatge d'error correspon a la diferència de tensió amplificada entre la tensió del punt de consigna del DAC i la tensió de sortida de retroalimentació.

Pas 2: Milloreu el rendiment en condicions de càrrega lleugera

Per a dispositius portàtils i portàtils, cal millorar el rendiment en condicions de poca càrrega per allargar la durada de la bateria. Moltes aplicacions portàtils i portables es troben en mode d’espera “de suspensió temporal” o “repòs” de baixa consum la major part del temps, només s’activen en resposta a l’entrada de l’usuari o a mesures periòdiques, de manera que minimitzeu el consum d’energia en mode d’espera. És la màxima prioritat.

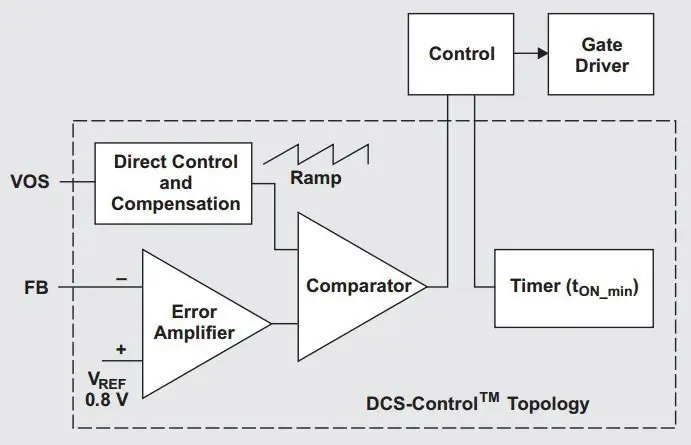

La topologia DCS-ControlTM (control directe a la transició sense costures al mode d’estalvi d’energia) combina els avantatges de tres esquemes de control diferents (és a dir, el mode d’histèresi, el mode de tensió i el mode de corrent) per millorar el rendiment en condicions de càrrega de llum, especialment la transició a O quan deixant l’estat de càrrega lleugera. Aquesta topologia admet els modes PWM per a càrregues mitjanes i pesades, així com el mode d’estalvi d’energia (PSM) per a càrregues lleugeres.

Durant el funcionament PWM, el sistema funciona a la seva freqüència de commutació nominal basada en la tensió d'entrada i controla el canvi de freqüència. Si el corrent de càrrega disminueix, el convertidor canvia al PSM per mantenir una alta eficiència fins que cau a una càrrega molt lleugera. A PSM, la freqüència de commutació disminueix linealment amb el corrent de càrrega. Els dos modes estan controlats per un bloc de control únic, de manera que la transició de PWM a PSM és perfecta i no afecta la tensió de sortida.

La figura 3 és un diagrama de blocs del DCS-ControlTM. El bucle de control pren informació sobre el canvi de tensió de sortida i la torna directament al comparador ràpid. El comparador estableix la freqüència de commutació (com a constant per a les condicions de funcionament en estat estacionari) i proporciona una resposta immediata als canvis de càrrega dinàmics. El bucle de retroalimentació de voltatge regula amb precisió la càrrega de CC. La xarxa de regulació compensada internament permet un funcionament ràpid i estable amb components externs petits i condensadors de baixa ESR.

Figura 3: Implementació de la topologia DCS-ControlTM al convertidor de buck TPS62130 (Font: Texas Instruments)

El convertidor de potència de commutació síncrona TPS6213xA-Q1 es basa en la topologia DCS-ControlTM i està optimitzat per a aplicacions POL d’alta densitat de potència. La freqüència de commutació típica de 2,5 MHz permet l’ús de petits inductors i proporciona una resposta transitòria ràpida i una alta precisió de voltatge de sortida. El TPS6213 funciona des d’un rang de voltatge d’entrada de 3V a 17V i pot subministrar fins a 3A de corrent continu entre 0,9V i 6V tensions de sortida.

Recomanat:

Recuperació de fonts d'alimentació de PC antigues: 12 passos (amb imatges)

Recuperació de fonts d’alimentació de PC antigues: des dels anys noranta, els ordinadors han envaït el món. La situació continua fins als nostres dies. Els ordinadors més antics, fins al 2014

Com solucionar els punts blancs i els píxels morts del projector BenQ JoyBee GP2: 5 passos

Com solucionar els punts blancs i els píxels morts del projector BenQ JoyBee GP2: teniu projectors DLP? Teníeu els punts blancs o els píxels morts a la pantalla del vostre projector DLP? No us preocupeu. Avui estic creant una publicació d’Instructables per compartir-vos la meva experiència sobre com solucionar els píxels morts del meu projector BenQ Joybee GP2. No obstant això, si

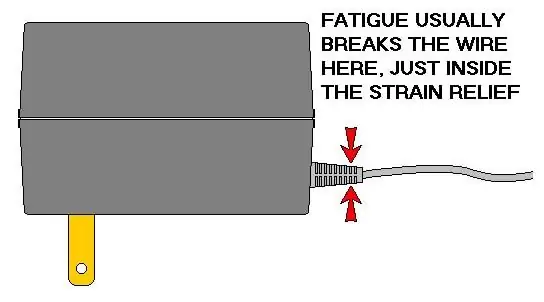

Reparació de fonts d'alimentació modulars: 6 passos

Reparació de fonts d'alimentació modulars: instruccions sobre com trencar el segell de les fonts d'alimentació modulars per solucionar el problema comú de trencaments de fatiga al cable, reparar els components interns o recuperar-los per a altres usos. Això infringirà les garanties, de manera que feu-ho només per a equips no coberts per cap

Distribuïu els vostres instructables, els temes del fòrum i els vostres preferits a Twitter i Facebook: 3 passos

Distribuïu els vostres instructables, els temes del fòrum i els vostres preferits a Twitter i Facebook: mitjançant els canals RSS del vostre compte i d'un parell de llocs web útils, és possible sindicar i compartir els vostres instructables, els temes del fòrum, els preferits i tota la resta de la vostra activitat a Instructibles a Facebook o Twitter. Aquesta és una gran manera

Instruccions per completar la maqueta del disseny de diapositives de via per elevar / baixar els reposapeus muntats al centre de les cadires de rodes elèctriques: 9 passos (amb ima

Instruccions per completar la maqueta del disseny de corredisses de via per a l’elevació / baixada dels reposapeus muntats al centre de les cadires de rodes elèctriques: s’eleven els reposapeus muntats al centre per col·locar-los sota el pou del seient i baixar-los per desplegar-los. A les cadires de rodes elèctriques del mercat no s’inclou un mecanisme per al funcionament independent de l’estiba i el desplegament del reposapeus, i els usuaris de PWC han expressat la necessitat