Taula de continguts:

- Pas 1: configureu la lògica programable de Zynq per al transmissor

- Pas 2: configureu la lògica programable de Zynq per al receptor

- Pas 3: configureu el controlador VDMA

- Pas 4: configureu la xarxa Nanorouter

- Pas 5: configureu el sistema de processament Zynq per a la transmissió de dades mitjançant Ethernet

- Pas 6: configureu el sistema de processament Zynq per a la recepció de dades mitjançant Ethernet

- Pas 7: connecteu les plaques Zybo a la font HDMI i al dissipador HDMI

- Pas 8: idees alternatives per millorar

- Pas 9: accessibilitat

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:14.

- Última modificació 2025-01-23 14:38.

Alguna vegada heu desitjat connectar el televisor a un PC o portàtil com a monitor extern, però no voleu tenir tots aquests molestos cables? Si és així, aquest tutorial és només per a vosaltres. Tot i que hi ha alguns productes que assoleixen aquest objectiu, un projecte de bricolatge és molt més satisfactori i potencialment més econòmic.

Aquest concepte és diferent de productes com el chromecast, ja que està pensat per substituir un cable HDMI que es connecta a un monitor en lloc de ser un dispositiu de transmissió.

El nostre projecte es va crear com a projecte final per a un curs de sistemes operatius en temps real a la Universitat Politècnica Estatal de Califòrnia, San Luis Obispo.

L’objectiu del projecte és utilitzar dues plaques Digilent Zybo per actuar com a interfície de comunicació sense fils entre un dispositiu transmissor HDMI (PC, blu-ray, etc.) a un dispositiu receptor HDMI (monitor d’escriptori, projector, TV, etc.).

Un Digilent Zybo es connectarà mitjançant HDMI al dispositiu transmissor i l’altre es connectarà mitjançant HDMI al dispositiu receptor.

La comunicació sense fils es realitzarà mitjançant una xarxa d’àrea local sense fils dedicada al transmissor i al receptor, sense ser encaminada a través d’un enrutador domèstic o d’un altre dispositiu d’aquest tipus. El mòdul sense fils utilitzat per a aquest projecte és el nanorouter tplink wr802n, un dels quals funciona com a punt d'accés per establir la xarxa i l'altre per operar com a client per connectar-se a la xarxa. Cada nanorouter es connectarà mitjançant un cable Ethernet a qualsevol placa Zybo. Quan es connecten a aquests encaminadors, els dispositius es comunicaran mitjançant TCP com si estiguessin connectats amb un sol cable ethernet (és a dir, l’única configuració necessària per establir una connexió és l’adreça IP del client).

Tot i que l’objectiu del projecte era facilitar un flux de vídeo de 1080x720 @ 60Hz, això no es va aconseguir a causa de les limitacions d’amplada de banda de la xarxa sense fils i la manca de compressió de vídeo en temps real per reduir les dades necessàries per enviar. En canvi, aquest projecte serveix com a marc per al desenvolupament futur per assolir aquest objectiu, ja que ha restringit severament les limitacions en la velocitat de fotogrames per transmetre correctament dades HDMI tal com es pretenia.

Requisits del projecte:

2 plaques de desenvolupament Digilent Zybo (han de tenir com a mínim un port HDMI)

2x cables HDMI

2x cables de microusb (per connectar Zybo a l'ordinador per al desenvolupament)

2x nanorouters tplink wr802n (inclosos els adaptadors d'alimentació de 2x microusb i presa de paret)

2x cables ethernet

*** Nota: aquest tutorial suposa familiaritat amb el paquet de disseny Vivado i experiència en la creació d'un nou projecte i disseny de blocs. ***

Pas 1: configureu la lògica programable de Zynq per al transmissor

El nostre enfocament per desenvolupar la lògica programable del transmissor era realitzar un pas hdmi-a-hdmi des del PC per supervisar-lo mitjançant dos blocs d'accés a la memòria directa de vídeo (VDMA), un per escriure i un per llegir.

Tots dos estan seleccionats per al mode de memòria intermèdia de 3 fotogrames de funcionament lliure (0-1-2). Com que el nucli de vídeo està optimitzat per a 60 fotogrames per segon, això vol dir que el VDMA escriurà o llegirà en un fotograma nou cada 16,67 ms en aquest ordre: 0, 1, 2, 0, 1, 2, 0, 1, 2. Les ubicacions de memòria DDR per a cada fotograma són diferents per als dos VDMA perquè ja no estan sincronitzades entre si. En canvi, s’utilitza un temporitzador de maquinari (TTC1), configurat per a 60 Hz, per sincronitzar el moviment de dades entre les dues ubicacions de memòria.

La imatge superior mostra 3 fotogrames, les seves dimensions i la quantitat de memòria que cadascun necessita (a la dreta del fotograma). Si assignem el VDMA d’escriptura a aquestes ubicacions de memòria, podem assignar les ubicacions de memòria VDMA llegides més enllà d’aquest conjunt, per exemple, començant per 0x0B000000. Cada fotograma està format per 1280 * 720 píxels i cada píxel es compon de 8 bits de vermell, verd i blau per a un total de 24 bits. Això significa que un marc està format per 1280 * 720 * 3 bytes (2,76 MB).

Dins del temporitzador IRQ, que es descriu a la configuració del controlador VDMA, gestionarà la còpia de dades entre les dues ubicacions de memòria VMDA. El VDMA proporciona un punter al marc actual on s’escriu o es llegeix. El marc està representat per un codi gris concret, que es converteix en programari. Les definicions de codi gris per a una configuració de memòria intermèdia de 3 fotogrames es poden trobar a la Guia del producte AXI VDMA a l’apèndix C.

Això ens permet copiar els continguts que s’escriuen a la memòria sense llegir-los des d’un marc que s’escriu actualment.

*** Tingueu en compte que el VDMA llegit no s'utilitza quan s'envien dades a través de la xarxa sense fils. L'únic propòsit és verificar el funcionament correcte de la còpia de memòria des del VMDA d'escriptura. El VMDA llegit s'hauria de desactivar. ***

Aquests són els passos per crear el bloc de disseny de transmissors:

- En crear un nou projecte, és una bona idea assignar un xip o placa al projecte. En aquest enllaç es descriu com afegir fitxers de tauler nou al directori Vivado i associar el tauler correcte al vostre projecte. Us serà útil en afegir el bloc del sistema de processament i en passar del maquinari al programari (costat SDK).

-

Afegiu els blocs següents:

- dvi2rgb

- Entrada de vídeo a Axi4-stream

- Controlador de temps

- axi4-stream a vid

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Assistent per al rellotge

- Constant

- Sistema de processament de Zynq

- En afegir el sistema de processament, feu clic a "Executa l'automatització de blocs" a la barra superior de color verd i assegureu-vos que l'opció "Aplica un preajust de placa" estigui seleccionada. Deixeu tota la resta per defecte.

- Les imatges de la finestra de configuració de cada bloc es poden trobar a les imatges anteriors. Si no veieu cap imatge per a una finestra concreta, només cal que la deixeu per defecte.

-

Comenceu a configurar el sistema de processament Zynq:

- A Configuració PS-PL AXI Non Secure Enable GP Master AXI, activeu la interfície M AXI GP0

- A la configuració PS-PL HP Slave AXI Interface, activeu HP0 i HP1

- A la configuració MIO Assegureu-vos que ENET0 està activat a Perifèrics d'E / S i, a continuació, Unitat de processador d'aplicacions, activeu Timer0

- A Clock Configuration PL Fabric Clocks, activeu FCLK_CLK0 i configureu-lo a 100 MHz.

- Feu clic a D'acord

- Abans de fer clic a "Executa l'automatització de la connexió", assegureu-vos de connectar els blocs de vídeo tal com es veu a la imatge de disseny del bloc TX anterior. Voldreu canviar el nom de la constant a VDD i establir el valor a 1. Connecteu els blocs de vídeo en conseqüència.

- Feu que el rellotge i els pins de dades HDMI TMDS siguin externs als blocs rgb2dvi i dvi2rgb

- Creeu un port d'entrada i sortida per al senyal de detecció de connexió en calent (HPD) i connecteu-los junts, es defineixen al fitxer de restriccions

-

El rellotge de píxels es recupera del TMDS_Clk_p, que es crea al fitxer de restriccions. Aquesta serà de 74,25 MHz d’acord amb la resolució de 720p. És important connectar el rellotge de píxels (des del bloc dvi2rgb) als pins següents:

- vid_io_in_clk (vid al bloc de flux axi)

- vid_io_out_clk (corrent axi al bloc vid out)

- clk (controlador de temps)

- PixelClk (rgb2dvi)

- *** Nota: Actualment, per activar la recuperació del rellotge de píxels, els connectors HDMI rx i tx han d'estar connectats a una font / pica activa. Una manera d’evitar-ho és separar els blocs de vídeo rx i tx en diferents dominis de rellotge (és a dir, generar un nou rellotge de 74,25 MHz per alimentar el bloc tx). ***

- A continuació, configureu l'assistent de rellotge de manera que tingueu una entrada de 100 MHz (font de memòria intermèdia global) i 3 rellotges de sortida a 50 MHz (rellotge AXI-Lite), 150 MHz (rellotge AXI4-Stream), 200 MHz (pin RefClk dvi2rgb).

- Connecteu el pin del sistema de processament FCLK_CLK0 a l'entrada de l'assistent del rellotge

- En aquest punt, feu clic a "Executa l'automatització de la connexió" a la barra verda de la part superior de la finestra de disseny. És una bona idea fer-ho per un bloc a la vegada i seguir la imatge de disseny del bloc TX anterior.

- L'eina intentarà afegir l'interconnexió AXI, que actua com a interconnexió mestre / esclau per als blocs que utilitzen el bus AXI-Lite (VDMA i GPIO).

- També afegirà AXI SmartConnect, que actua com a interconnexió mestre / esclau per a les interfícies de processador AXI4-Stream i High Performance que utilitza el VDMA (Stream to Memory Map i viceversa).

- L'eina també afegirà un restabliment del sistema del processador. Assegureu-vos que només estigui connectat als blocs relacionats amb el VDMA, GPIO i el processador. No el connecteu a cap bloc de vídeo (és a dir, dvi2rgb, controlador de temps, vídeo per transmetre, etc.)

- Un cop finalitzada l'automatització de les connexions, verifiqueu que les connexions coincideixin amb la de la imatge de disseny del bloc TX. Notareu un bloc ILA del sistema addicional que no s’ha mencionat. Això només és per a la depuració i no és necessari per ara. Utilitza el reinici del processador de 150 M, de manera que tampoc no és necessari. En qualsevol lloc que vegeu petits "errors" verds als autobusos, això és a causa de l'ILA i es pot ignorar.

- L'últim pas és fer clic amb el botó dret del ratolí sobre el disseny del bloc a l'arbre de fonts del projecte i seleccionar "Crea HDL Wrapper". Si teniu previst afegir lògica a l’embolcall, se sobreescriurà cada vegada que se selecciona.

- Consulteu la secció Configuració del controlador VDMA per obtenir detalls al costat de l'SDK.

Rellotges i restabliments

He descobert que els aspectes més importants de qualsevol projecte de lògica programable són la consideració acurada dels dominis de rellotge i els senyals de restabliment. Si els teniu configurats correctament, teniu una bona oportunitat per aconseguir que el vostre disseny funcioni.

Rellotge de píxels i temporització bloquejada

Per comprovar que certs senyals estan actius, és una bona idea lligar aquests senyals als LED (rellotges, restabliments, panys, etc.). Dos senyals que he trobat útils per rastrejar a la placa del transmissor eren el rellotge de píxels i el senyal "bloquejat" del bloc de sortida de vídeo AXI4-Stream, que us indica que la sincronització del vídeo s'ha sincronitzat amb el controlador de temporització i la font de vídeo. dades. He afegit una mica de lògica a l’embolcall de blocs de disseny que fa un seguiment del rellotge de píxels mitjançant el senyal PixelClkLocked del bloc dvi2rgb com a restabliment. He adjuntat el fitxer com hdmi_wrapper.v aquí. El fitxer de restriccions també s'adjunta aquí.

Pas 2: configureu la lògica programable de Zynq per al receptor

El bloc de lògica programable per al receptor és més senzill. La diferència clau, a part dels blocs d’entrada hdmi que falten, és l’absència d’un rellotge de píxels recuperat. Per aquest motiu, hem de generar el nostre a partir de l'assistent del rellotge. Aquest disseny s'ha de fer en un projecte separat del transmissor. Per als nostres propòsits, el projecte receptor va seguir la placa Zybo 7Z-20, mentre que el transmissor va seguir la placa Z7-10. Els FPGA dels taulers són diferents, així que … aneu amb compte.

Aquests són els passos per crear el bloc de disseny del receptor:

-

Afegiu els blocs IP següents al vostre disseny:

- Controlador de temps

- AXI4-Stream a sortida de vídeo

- RGB a DVI

- AXI VDMA

- AXI GPIO

- Sistema de processament

- Assistent per al rellotge

- Constant (VDD definit a 1)

- Seguiu el mateix patró per configurar aquests blocs que el transmissor. Aquí s’inclouen imatges de les notables diferències de configuració. Els altres segueixen sent els mateixos que el transmissor.

- Configureu el VDMA per a aquest disseny només com a canal de lectura. Desactiveu el canal d'escriptura.

-

L'assistent de rellotge s'hauria de configurar per a les sortides següents:

- clk_out1: 75 MHz (rellotge de píxels)

- clk_out2: 150 MHz (rellotge de transmissió)

- clk_out3: 50 MHz (rellotge axi-lite)

- Connecteu els blocs de vídeo tal com es mostra a la imatge de disseny del bloc RX.

- A continuació, executeu l'automatització de la connexió, que afegirà els blocs AXI Interconnect, AXI SmartConnect i System Reset i intentarà fer les connexions adequades. Aneu lentament aquí per assegurar-vos que no realitza connexions no desitjades.

- Feu que el rellotge i els pins de dades HDMI TMDS siguin externs al bloc rgb2dvi

- No cal cap senyal d’endoll calent en aquest disseny.

Pas 3: configureu el controlador VDMA

La configuració dels diferents blocs que es configuren a través de la interfície AXI-Lite es fa millor utilitzant els projectes de demostració inclosos amb el BSP com a referència. Després d’exportar el maquinari de disseny i d’iniciar l’SDK de Vivado, voldreu afegir un nou paquet de suport per a la placa i incloure la biblioteca lwip202 a la finestra de configuració de BSP. Obriu el fitxer de fitxer system.mss des del BSP i veureu els controladors de perifèrics presents al disseny del bloc. L'opció "Importa exemples" us permet importar projectes de demostració que utilitzen aquests perifèrics i mostrar-vos així com configurar-los al programari mitjançant els controladors Xilinx disponibles (vegeu la imatge adjunta).

Aquest va ser el mètode utilitzat per configurar el VDMA, el temporitzador i la interrupció i el GPIO. Aquí s’inclou el codi font de transmissió i recepció. Les diferències són gairebé exclusivament a main.c.

*** NOTA: Atès que el sistema no és completament funcional en el moment d'escriure aquest tutorial, el codi font d'aquesta secció no inclou el codi de xarxa sense fils. Cal combinar diversos errors com a resultat de combinar els projectes de transmissió / recepció del nucli de vídeo amb els projectes de transmissió / recepció de la xarxa. Per tant, aquest tutorial els tracta de moment per separat. ***

Funció TX Interrupt Handler (IRQHandler)

Aquesta funció llegeix els codis grisos proporcionats pels VDMA de lectura i escriptura mitjançant els blocs GPIO. Els codis grisos es converteixen en decimals i s’utilitzen per seleccionar la ubicació de memòria base del marc del marc actual. El fotograma copiat és el fotograma anterior al que escriu el VDMA (per exemple, si el VDMA escriu al fotograma 2, copiem el fotograma 1; si s’escriu al fotograma 0, ajustem i llegim del fotograma 2).

La funció només captura cada sisè fotograma per reduir la velocitat de fotogrames a 10 Hz en lloc de 60 Hz. El límit superior de la xarxa és de 300 Mbps. A 10 fotogrames per segon es requereix un ample de banda de 221,2 Mbps.

Si comenteu o no comenteu dues línies en aquesta funció, l’usuari podrà canviar al mode passthru HDMI a efectes de depuració / prova (es comenta el codi per indicar les línies adequades). Actualment copia el marc a una ubicació de memòria que utilitza el codi ethernet.

Funció RX Interrupt Handler (IRQHandler)

Aquesta funció és molt similar a la funció TX, però copia des d'un FIFO de 2 memòries intermèdies que utilitza ethernet per escriure dades entrants. El codi ethernet indica a quin fotograma s’està escrivint del FIFO, les dades es copien des del fotograma oposat. Les dades es copien al marc directament darrere del que està llegint el VDMA per evitar que es trenquin.

Pas 4: configureu la xarxa Nanorouter

Per crear una xarxa mitjançant els nanorouters TPlink, enceneu-los individualment i connecteu-vos al SSID wifi predeterminat per als dispositius. Podeu trobar més informació sobre els paràmetres de configuració d’aquest dispositiu en concret a través del manual d’usuari del dispositiu.

Configureu un dels dispositius com a punt d'accés, que actuarà com a connexió principal per a la xarxa. Assegureu-vos de posar un nom a la xarxa i anotar-ne el nom i desactivar DHCP (no volem que l’encaminador configure les adreces IP de manera dinàmica, volem que les plaques Zybo d’emissor i receptor d’escenari configurin les seves adreces IP per tal que siguin coherents). Després de configurar-lo, assegureu-vos que el dispositiu es reiniciï i estableixi aquesta xarxa.

Configureu l’altre dispositiu com a client i assegureu-vos que es connecti al SSID de xarxa que heu configurat amb el primer nanorouter. Una vegada més, assegureu-vos que DHCP estigui inhabilitat per al client.

Un cop el client hagi acabat i reiniciat, hauria de connectar-se al nanorouter del punt d’accés (si no és així, és probable que hi hagi un problema a la configuració d’un dels dispositius). Notareu que la llum LED del client serà sòlida un cop s'hagi connectat al punt d'accés.

És probable que el LED de nanorouter del punt d’accés continuï parpellejant en aquest punt, està bé! La llum intermitent significa que no està connectat a cap altre dispositiu des del seu port Ethernet i, un cop connectat a un Zybo configurat, el LED es mantindrà sòlid indicant una connexió de xarxa satisfactòria.

Ara que tenim la configuració dels nostres nanorouters, tenim una xarxa sense fils que ens permetrà comunicar-nos. Una nota important és que el nostre mètode de configuració per als nanorouters (com a punt d’accés i client) ens permet comunicar-nos des de la placa Zybo transmissora a la placa Zybo receptora com si els dos estiguessin connectats amb un sol cable Ethernet. Això fa que la configuració de la nostra xarxa sigui menys difícil, ja que l’alternativa probablement incorporaria la configuració de les plaques Zybo per connectar-se explícitament al servidor juntament amb la connexió prevista.

Un cop configurats els dos dispositius, els nanorouters es configuren i estan preparats per implementar-se a la vostra xarxa WIDI. No hi ha cap emparellament específic entre els nanorouters i les plaques Zybo, ja que el punt d’accés o el client funcionaran per al dispositiu de transmissió o recepció.

Pas 5: configureu el sistema de processament Zynq per a la transmissió de dades mitjançant Ethernet

Per transmetre les dades HDMI d’una placa Zybo a l’altra, hem d’incorporar un protocol Ethernet amb el nostre controlador VDMA. El nostre objectiu aquí és transmetre marcs de vídeo individuals a través del perifèric Ethernet del sistema de processament, a un ritme establert que sigui coherent amb l’amplada de banda de la nostra xarxa. Per al nostre projecte, hem utilitzat TCP proporcionat per l'API LwIP de metall nu. Atès que tots dos membres del projecte tenen una experiència relativament inexperta en les utilitats de xarxa, aquesta tria es va fer sense reconèixer completament les implicacions i les limitacions implicades amb TCP. El principal problema amb aquesta implementació va ser l’amplada de banda limitada i el fet que realment no està dissenyada amb la finalitat de generar grans volums de dades. Més endavant es parlarà de solucions alternatives per substituir TCP i millorar aquest projecte.

Una breu descripció de TCP amb LwIP: les dades s’envien per la xarxa en paquets de mida tcp_mss (mida màxima del segment TCP), que sol ser de 1460 bytes. Cridar tcp_write agafarà algunes dades referenciats per un punter i configurarà pbufs (buffers de paquets) per contenir les dades i proporcionar una estructura per a les operacions TCP. La quantitat màxima de dades que es poden posar a la cua alhora es defineix com tcp_snd_buf (espai de memòria intermèdia del remitent TCP). Com que aquest paràmetre és un nombre de 16 bits, estem limitats a una mida de memòria intermèdia d’enviament de 59695 bytes (hi ha una mica de farciment obligatori a la memòria intermèdia d’enviament). Una vegada que les dades s'han posat a la cua, es crida a tcp_output per començar a transmetre les dades. Abans d'enviar el següent segment de dades, és imprescindible que tots els paquets anteriors s'hagin transmès amb èxit. Aquest procés es fa mitjançant la funció recv_callback, ja que aquesta és la funció que es diu quan es veu l'acceptació des del receptor.

Utilitzar els exemples de projectes a Vivado SDK és molt útil per aprendre com funciona LwIP TCP i és un bon punt de partida per començar un nou projecte.

El procediment per al dispositiu de transmissió WiDi és el següent:

- Inicialitzeu la xarxa TCP mitjançant les trucades de funció de controlador LWIP de metall nu.

- Especifiqueu les funcions de devolució de trucada necessàries per a les operacions de xarxa.

- Connecteu-vos al receptor WiDi connectant-vos a la seva adreça i port IP (la nostra configuració: IP del receptor és 192.168.0.9, connecteu-vos al port 7).

- Quan el temporitzador del controlador VDMA caduca, introduïu el TX ISR.

- Determineu la memòria intermèdia de trama actual per accedir basant-vos en el codi gris VDMA

- Posar en cua el primer segment de dades al buffer d’enviament TCP

- Sortiu les dades i actualitzeu les variables locals per fer un seguiment de la quantitat de dades que s’han enviat del marc actual.

- En arribar a la devolució de trucada rebuda (la trucada de funció realitzada després que el transmissor obtingui un reconeixement de la recuperació de dades), feu una cua al següent segment de dades.

- Repetiu els passos 7 i 8 fins que s'hagi enviat tot el marc.

- Torneu a un estat d'inactivitat per esperar a la següent interrupció del temporitzador per indicar que un nou marc està a punt (Torneu al pas 4).

Assegureu-vos de configurar la configuració del paquet de suport del tauler LwIP tal com es mostra a la imatge superior. Tots els valors són per defecte excepte tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Tingueu en compte també que es pot aconseguir una depuració detallada canviant els paràmetres BSP del grup debug_options.

Pas 6: configureu el sistema de processament Zynq per a la recepció de dades mitjançant Ethernet

La placa de desenvolupament Zybo que actuarà com a receptor sense fils funcionarà de manera similar al dispositiu transmissor. La configuració del paquet de suport de la placa per a LwIP serà idèntica a la del pas anterior.

El dispositiu inclourà paquets que continguin els segments de fotogrames de vídeo del nanorouter i copiarà les dades de fotogrames de vídeo a l’espai de memòria intermèdia de triple fotograma per al VDMA receptor. Per tal d’evitar sobreescriure qualsevol dada, s’utilitza una memòria intermèdia de dades doble (ens referirem com a memòria intermèdia de xarxa) quan es recopilen dades del nanorouter, de manera que el trànsit de xarxa pugui continuar transmetent-se mentre es copia el fotograma de vídeo complet anterior al Memòria intermèdia VDMA.

El procediment per al dispositiu de recepció de WiDi requereix dues tasques, una de les quals és la recepció de dades Ethernet, i l’altra copiar fotogrames de vídeo des de la memòria intermèdia de xarxa a la memòria intermèdia de tres fotogrames del VDMA.

Tasca de recepció Ethernet:

- Inicialitzeu la xarxa TCP mitjançant les trucades de funció de controlador LWIP de metall nu (configuració amb l'adreça IP a la qual es connectarà el transmissor, 192.168.0.9 a la nostra)

- Especifiqueu les funcions de devolució de trucada necessàries per a les operacions de xarxa.

- Després de rebre el paquet ethernet, copieu les dades del paquet a la memòria intermèdia de xarxa actual i augmenteu les dades acumulades actuals.

- Si el paquet omple el buffer de marcs de xarxa, continueu amb els passos 5 i 6. En cas contrari, torneu al pas 3 d'aquesta tasca.

- senyal que la tasca de memòria intermèdia de triple fotograma VDMA hauria de copiar-se de la memòria intermèdia de xarxa acabada.

- Canvieu a l’altre memòria intermèdia de xarxa i continueu recopilant dades per Ethernet.

- Inactiu fins que es rep un nou paquet Ethernet (pas 3).

Copieu la memòria intermèdia de xarxa a la memòria intermèdia triple de VDMA:

- Quan el temporitzador del controlador VDMA caduca, introduïu el RX ISR.

- Determineu la memòria intermèdia de trama actual per accedir basant-vos en el codi gris VDMA.

- Determineu quin buffer de xarxa es copiarà al buffer VDMA i copieu aquestes dades

Pas 7: connecteu les plaques Zybo a la font HDMI i al dissipador HDMI

Ara connecteu els cables HDMI tant per al receptor com per al transmissor, programeu els FPGA i executeu el sistema de processament. És probable que la velocitat de fotogrames sigui molt lenta, a causa de la immensa sobrecàrrega en l'operació LwIP i l'amplada de banda limitada. Si hi ha algun problema, connecteu-vos mitjançant UART i intenteu identificar qualsevol advertència o error.

Pas 8: idees alternatives per millorar

Un gran problema d’aquest projecte va ser la quantitat de dades necessàries per enviar per wifi. Això s'esperava, però hem subestimat l'impacte que això tindria i es traduirà en una explosió d'imatges a la pantalla en lloc d'un feed de vídeo. Hi ha diverses maneres de millorar aquest projecte:

- Compressió de vídeo en temps real. La compressió del canal d’entrada de vídeo entrant per fotograma reduiria considerablement la quantitat de dades necessàries per enviar per la xarxa. L'ideal seria fer-ho en maquinari (que no és una tasca fàcil), o bé es podria fer en programari utilitzant l'altre nucli ARM per executar algoritmes de compressió (això necessitaria una anàlisi addicional per assegurar que el temps funciona). Hi ha alguns components de compressió de vídeo en temps real de codi obert que hem trobat al web, però la majoria són IP.

- Implementació del flux Ethernet al maquinari en lloc del programari. Hi havia un munt de despeses generals a causa de la manca d’espai disponible per fer cua de dades de sortida al transmissor, a causa de la limitació de la mida del segment. Un procés molt més eficient és utilitzar l’IP Ethernet AXI amb un buffer FIFO o DMA per alimentar-hi dades. Això reduiria l’equipatge addicional de LwIP TCP i permetria més flux de dades.

Pas 9: accessibilitat

El producte resultant d’aquest projecte WiDi hauria de ser un parell de dispositius completament integrat i compacte que un usuari pugui connectar a qualsevol font HDMI i, a continuació, enfonsar l’alimentació de vídeo a una pantalla amb capacitat HDMI sense fils. Els dispositius inclourien el SoC Zynq-7000 que es troba a la placa de referència Zybo i incorporaria el maquinari de xarxa que es troba als nanoencaminadors TP-Link. Idealment, l'usuari seria capaç de controlar el mòdul de transmissió des d'una ubicació discreta dins del sistema operatiu objectiu, amb poca necessitat d'una capacitat tècnica significativa.

Seguretat i connectivitat

Els dispositius també haurien d’incorporar seguretat de capa de transport (TLS) i tenir una capacitat de connexió automàtica limitada, tant amb finalitats de privadesa. La intenció dels dissenyadors és que la connexió amb una pantalla a través d’una interfície sense fils sigui una acció deliberada en nom de l’usuari per evitar l’emissió errònia de material sensible.

Estat actual

Fins a aquest punt, l’estat del projecte continua essent un treball en curs. Per tal que l’usuari actual del punt final es pugui beneficiar d’aquest tutorial, ha de tenir una bona comprensió tècnica del disseny de sistemes incrustats i ha de tenir una certa familiaritat amb el maquinari programable i el programari incrustat que treballen junts.

Les dades que s’envien per la xarxa no estan xifrades en aquest moment i se suposa que és una transmissió en brut de paquets TCP / IP.

El projecte del nucli de vídeo s'ha provat amb èxit tant per transmetre com per rebre. D'altra banda, es va establir la connexió sense fils entre dues plaques zybo i es van enviar les dades del marc de prova amb èxit. Tot i així, és necessari combinar el codi de xarxa a cada projecte bàsic de vídeo i provar la transmissió de fotogrames de vídeo reals.

Recomanat:

Tauler d’anuncis sense fils (Bluetooth): 5 passos (amb imatges)

Tauler d’anuncis sense fils (Bluetooth): en aquest món modern on tot està digitalitzat, per què no el tauler d’anuncis convencional té un nou aspecte? Per tant, podem fer un tauler d’anuncis controlat per Bluetooth que és molt senzill. Aquesta configuració es pot utilitzar en lloc d’avis estàtics tauler com a universitats / a

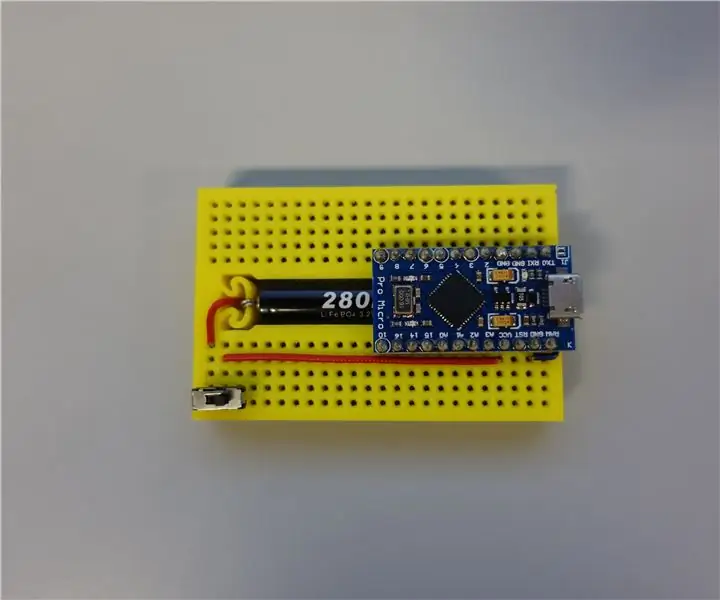

Taula de pa del tauler de desenvolupament: 12 passos (amb imatges)

Taula de pa del tauler de desenvolupadors: aquest manual d’instruccions mostra com crear una tauler de pa a mida per al tauler de programació

Construeix el teu propi tauler de desenvolupament: 8 passos (amb imatges)

Construeix el teu propi tauler de desenvolupament: aquest instructiu us mostrarà com construir el vostre propi tauler de desenvolupament des de zero. Aquest mètode és senzill i no necessita cap eina avançada, fins i tot podeu fer-ho a la taula de la cuina. Això també proporciona una millor comprensió de com Ardruinos i

UDuino: Tauler de desenvolupament compatible amb Arduino de molt baix cost: 7 passos (amb imatges)

UDuino: Taula de desenvolupament compatible amb Arduino de molt baix cost: les plaques Arduino són ideals per prototipar. No obstant això, són bastant cars quan teniu diversos projectes simultanis o necessiteu moltes plaques de control per a un projecte més gran. Hi ha algunes alternatives fantàstiques i econòmiques (Boarduino, Freeduino), però

Introduïu un timbre sense fils en un interruptor d'alarma sense fils o un interruptor d'encesa / apagat: 4 passos

Introduïu un timbre sense fils en un interruptor d'alarma sense fils o en un interruptor d'encès / apagat: recentment he construït un sistema d'alarma i l'he instal·lat a casa. Vaig fer servir interruptors magnètics a les portes i els vaig connectar a través de les golfes: les finestres eren una altra història i el cablejat dur no era una opció. Necessitava una solució sense fils i això és