Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:15.

- Última modificació 2025-01-23 14:38.

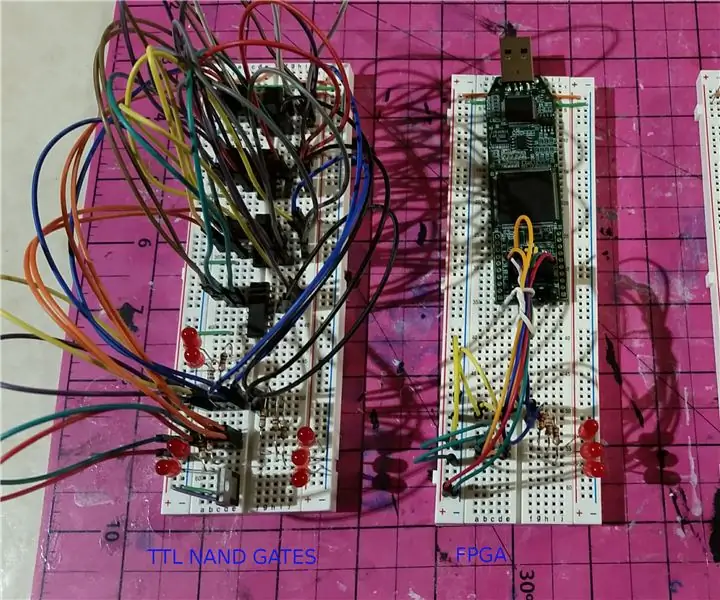

Dissenyar circuits lògics de maquinari pot ser divertit. La manera de fer-ho de la vella escola era amb les portes NAND, sobre una taula de pa, connectades amb cables de pont. Això encara és possible, però no es necessita gaire abans que el nombre de portes s’escapi de les mans. Una opció més recent és utilitzar un FPGA (Field Programmable Gate Array). Aquests xips es poden reconnectar per convertir-se en qualsevol circuit lògic digital que pugueu dissenyar, però no són barats i estan fàcilment disponibles. Vaig a mostrar com es pot substituir aquest FPGA per un xip Atmega barat d'un Arduino UNO, posant efectivament el circuit digital en un paquet DIP, que és molt amable per a la taula de treball.

Pas 1: Dissenyeu el circuit que representarà el "FPGA"

Construiré un sumador de 2 bits + 2 bits. Es necessiten dos parells de pins d'entrada lògics i surt un triplet de pins de sortida.

Per fer-ho amb les portes NAND, consulteu l’esquema de la imatge. Necessita 14 portes NAND. Vaig fer servir quatre xips TTL de quatre portes NAND i els vaig connectar a la taula de pa.

He afegit alguns LEDs (no oblideu les resistències de limitació d’actualitat) per mostrar quan els pins d’entrada i sortida estaven encès (alt) i quan estaven apagats (baix). Per conduir els pins d'entrada, els vaig passar al rail de terra o al rail de potència positiva.

Aquest circuit funciona, però ja ocupa 4 xips TTL i és un niu de filferro de rata. Si calguessin més bits, hi hauria més taules de pa i més ponts. Molt ràpidament la mida del circuit se’ls escaparia de les mans.

En una nota lateral, quan es treballa amb portes TTL, no emeten exactament 0V ni 5V com es podria esperar. Sovint produeixen al voltant de 3 V per "alt", però el voltatge exacte es troba en un rang molt ampli. El mateix circuit que utilitza els xips equivalents CMOS tindria millors oscil·lacions exactes de 0V a 5V exactament.

Pas 2: introduïu el FPGA

Un FPGA és un xip fantàstic que es pot convertir literalment en qualsevol combinació de portes lògiques, connectades en qualsevol combinació. Un dissenya el "circuit" en un llenguatge de disseny de maquinari (HDL). Hi ha diversos idiomes, un dels quals es diu Verilog. El fitxer.v de la imatge és l'equivalent de Verilog del sumador de dos bits. El fitxer.pch que hi ha a sota també és necessari per assignar els pins d'entrada i sortida anomenats al fitxer verilog als pins de maquinari reals del xip.

En aquest cas, estic fent servir una placa de desenvolupament iCEstick de Lattice Semiconductors (https://www.latticesemi.com/icestick). El xip FPGA real és un iCE40HX-1k, amb una mica més de 1000 portes, que poden convertir-se en qualsevol porta lògica. Això significa que cada porta pot ser una porta NAND o una porta OR, NO porta, NOR, XOR, etc. A més, cada porta pot gestionar més de dues entrades. Això és específic per a cada fabricant, però a l'iCE40 cada porta pot gestionar 4 entrades. Per tant, cada porta és molt més capaç que les dues portes NAND d’entrada.

Vaig haver d'assignar els 4 pins d'entrada i els 3 pins de sortida als pins físics 91, 90, 88, 87, 81, 80 i 79 respectivament. Això és específic del xip fpga i de la placa de ruptura on es troba, i de com es connecten aquests pins al port PMOD. Està disponible als fulls de dades d'aquesta placa FPGA.

Lattice proporciona la seva pròpia cadena d’eines per sintetitzar circuits (l’equivalent a FPGA per a la compilació per a CPU) de circuits de Verilog, però he utilitzat la cadena d’eines lliure open source icestorm (https://www.clifford.at/icestorm/). Les instruccions d'instal·lació estan disponibles en aquest lloc. Amb icestorm instal·lat i el fitxer verilog i pcf, les ordres per carregar aquest circuit al FPGA són:

yosys -p "synth_ice40 -blif twoBitAdder.v" twoBitAdder.blif

arachne-pnr -d 1k -p iCEstick.pcf twoBitAdder.blif -o twoBitAdder.asc

icepack twoBitAdder.asc twoBitAdder.bin

iceprog twoBitAdder.bin

Funciona molt bé, però incloure l’enviament d’aquest iCEstick costarà uns 30 dòlars. Aquesta no és la manera més barata de construir un circuit digital, però és potent. Té més de 1000 portes i per a aquest petit circuit només en fa servir 3. L'equivalent a la porta NAND utilitzava 14 portes. Això es deu al fet que cada porta es pot convertir en qualsevol tipus de porta, i cada porta és en realitat una porta d’entrada de 4. Cada porta pot fer més. Si necessiteu més portes, l’iCEstick té un germà gran amb 8.000 portes, que costa aproximadament el doble. Altres fabricants tenen altres ofertes, però el preu pot augmentar bastant.

Pas 3: de FPGA a Arduino

Els FPGA són excel·lents, però poden ser cars, difícils d’aconseguir i no són molt adequats per a la taula de pa. Un xip econòmic i econòmic és l'Atmega 328 P, que ve en un paquet DIP net, perfecte per a la pràctica de taulers. També es pot obtenir per uns 4 dòlars. Aquest és el cor de l’Arduino UNO. Per descomptat, podríeu fer servir tota l’ONU, però ser barat, podem treure l’Atmega 328 P de l’ONU i utilitzar-lo per si sol. Vaig fer servir la placa UNO com a programador per a l'Atmega.

En aquest moment el necessitareu

1. Un Arduino UNO, amb la CPU Atmega 328P extraïble.

2. Un altre Atmega 328P amb el carregador d'Arduino pre-cremat, per substituir el que estem a punt de treure de la UNO. (Opcional suposant que encara vulgueu tenir una ONU útil).

L’objectiu és convertir el fitxer verilog en un projecte arduino que es pugui carregar al 328P. Arduino es basa en C ++. Convenientment, hi ha un traductor de Verilog a C ++, anomenat Verilator (https://www.veripool.org/wiki/verilator). Verilator està pensat per ser utilitzat pels dissenyadors de maquinari que necessiten simular els seus dissenys abans de comprometre'ls amb maquinari car. La creu Verilator compila el verilog a C ++, i l'usuari proporciona un arnès de prova per proporcionar senyals d'entrada simulats i enregistrar els senyals de sortida. L’utilitzarem per aplegar el disseny del verilog a l’Atmega 328P mitjançant la cadena d’eines Arduino.

Primer instal·leu Verilator. Seguiu les instruccions a

Instal·leu també l'IDE Arduino i proveu que es pugui connectar a l'Arduino UNO per USB.

Utilitzarem el mateix fitxer de verilog que per a l’FPGA, excepte que cal canviar els noms dels pins. He afegit un subratllat (_) al començament de cadascun. Això és necessari perquè les biblioteques arduino inclouen un fitxer de capçalera que tradueix coses com B0, B001, etc., a nombres binaris. Els altres noms dels pins d'entrada haurien estat bé tal qual, però B0 i B1 haurien provocat un error en la construcció.

Al directori que conté twoBitAdder.v i iCEstick.pcf, executeu el següent:

verilator -Wall --cc twoBitAdder.v

Això crearà un subdirectori anomenat obj_dir que conté diversos fitxers nous. Només necessitem els fitxers de capçalera i cpp, VtwoBitAdder.h, VtwoBitAdder.cpp, VtwoBitAdder_Syms.h i VtwoBitAdder_Syms.cpp.

A l’IDE Arduino, creeu un nou esbós anomenat twoBitAdder.ino. Això crearà el fitxer ino en un directori nou també anomenat twoBitAdder, dins del directori del quadern de dibuixos Arduino. Copieu els fitxers VtwoBitAdder.h i VtwoBitAdder.cpp a aquesta carpeta twoBitAdder de la carpeta Arduino.

Ara copieu els fitxers de capçalera de la instal·lació del verificador.

cp / usr / local / share / verilator / include / verilated *.

finalment copieu a la biblioteca std c ++ a https://github.com/maniacbug/StandardCplusplus. Segons les seves instruccions d'instal·lació "S'instal·la com una biblioteca Arduino normal. Desempaqueteu el contingut de la distribució a la carpeta" biblioteques "del vostre quadern de dibuixos. Per exemple, el meu quadern de dibuixos es troba a / home / maniacbug / Source / Arduino, de manera que aquesta biblioteca es troba a / home / maniacbug / Source / Arduino / libraries / StandardCplusplus.

Assegureu-vos de restablir l'IDE Arduino després d'instal·lar-lo."

Ara substituïu el contingut de twoBitAdder.ino pel contingut proporcionat en aquest pas. Es tracta d’un arnès de prova que espera el verilador, que configura els pins d’entrada / sortida, i al bucle, llegeix els pins d’entrada, els alimenta al VtwoBitAdder (la versió traduïda del nostre circuit), després llegeix les sortides de VtwoBitAdder i aplica als pins de sortida.

Aquest programa hauria de compilar-se i executar-se a Arduino UNO.

Pas 4: d'Arduino al xip DIP en una placa de pa

Ara que el programa s’executa a l’Arduino, ja no necessitem la mateixa placa Arduino. Tot el que necessitem és la CPU.

Traieu l'Atmega 328P amb cura del sòcol Arduino UNO i, opcionalment, inseriu-ne la substitució.

Col·loqueu l'Atmega 328P a la pissarra. Poseu el final amb el divot apuntant cap amunt a la taula de pa. El pin 1 és el pin superior esquerre. El pin 2 és el següent cap avall, i així successivament fins al pin 14 que es troba a la part inferior esquerra. A continuació, el pin 15 es troba a la part inferior dreta i els pins 16 a 28 tornen a comptar per la part dreta del xip.

Connecteu els pins 8 i 22 a terra.

Connecteu el pin 7 a VCC (+ 5V).

Connecteu un cristall de quars de 16 MHz entre els pins 9 i 10. També un condensador petit (22pF) entre el pin 9 i el terra, i entre el pin 10 i el terra. Això proporciona a l'Atmega 328P la velocitat de rellotge de 16 MHz. Hi ha instruccions en altres llocs sobre com ensenyar al 328P a fer servir el rellotge intern de 8 MHz que permetria estalviar un parell de parts, però això frenaria el processador.

Els ports 5, 6, 7 i 8 d'Arduino GPIO, que hem utilitzat per als pins d'entrada, són en realitat els pins físics 11, 12, 13, 14 de l'Atmega 328P. Aquests serien els quatre passadors inferiors de l’esquerra.

Els ports 11, 10 i 9 d'Arduino GPIO, que hem utilitzat per als pins de sortida, són en realitat els pins físics 17, 16 i 15 de l'Atmega 328P. Aquests serien els tres pins inferiors de la dreta.

Vaig connectar els LEDs a aquests pins com abans.

Pas 5: Conclusió

Els xips TTL funcionen, però es necessiten molts per construir qualsevol cosa. Els FPGA funcionen molt bé, però no són barats. Si podeu viure amb menys pins IO i una velocitat inferior, és possible que un Atmega 328P sigui el vostre xip.

Algunes coses a tenir en compte:

FPGA:

Pro

- Pot gestionar senyals d'alta velocitat. Com que no hi ha processadors de coll d'ampolla cap CPU per a una instrucció cada vegada, el factor limitant és el retard de propagació a través de les portes del circuit donat. En molts casos, això pot ser molt més ràpid que el rellotge subministrat amb el xip. Per al meu disseny, el retard calculat hauria permès que el twoBitAdder respongués a uns 100 milions de canvis en els valors d’entrada per segon (100 MHz), tot i que el rellotge incorporat només és un cristall de 12 MHz.

- A mesura que el disseny es fa més complex, el rendiment dels circuits existents no es degrada (gaire). Com que afegir circuits al teixit és simplement posar alguna cosa nova en immobles no utilitzats, no afecta els circuits existents.

- Depenent de l'FPGA, el nombre de pins d'E / S disponibles pot ser molt elevat i, generalment, no tenen cap finalitat concreta.

Con

- Pot ser costós i / o difícil d’aconseguir.

- Normalment es presenta en un paquet BGA que requereix algun tipus de tauler per treballar amb el xip en qualsevol projecte amateur. Si el construïu en un disseny amb un PCB SMT multicapa personalitzat, això no és un problema.

- La majoria dels fabricants de FPGA proporcionen el seu propi programari de disseny de font tancat, que en alguns casos pot costar diners o tenir una data de caducitat de la llicència.

Arduino com a FPGA:

Pro

- Barat i fàcil d’aconseguir. Només cal que cerqueu atmega328p-pu a Amazon. Haurien de ser d’uns 4 dòlars / peça. Diversos venedors els venen en lots de 3 o 4.

- Es tracta d’un paquet DIP, que significa que s’adapta perfectament a una taula de treball amb els seus pins externs.

- Aquest és un dispositiu de 5V, que pot facilitar la interfície amb altres dispositius de 5V.

Con

- L'ATMEGA328P té un nombre limitat de pins d'E / S (23), i alguns d'ells estan reservats per a tasques específiques.

- A mesura que augmenta la complexitat del circuit, la quantitat de codi executat en el mètode del bucle Arduino augmenta, la qual cosa significa que la durada de cada cicle és més llarga.

- Fins i tot si la complexitat del circuit és baixa, cada cicle requereix moltes instruccions de la CPU per obtenir els valors del pin d'entrada i escriure els valors del pin de sortida i tornar a la part superior del bucle. Amb un cristall de 16 MHz, fins i tot amb una instrucció per cicle de rellotge, el bucle no funcionarà més d’un milió de vegades per segon (1 MHz). Per a la majoria de projectes electrònics aficionats, això és molt més ràpid del necessari.

Recomanat:

NodeMCU Lua Tauler barat de 6 $ amb registre de temperatura i humitat MicroPython, estadístiques Wifi i mòbils: 4 passos

NodeMCU Lua Tauler barat de 6 $ amb registre de temperatura i humitat de MicroPython, estadístiques de Wi-Fi i mòbils: bàsicament és una estació meteorològica en núvol, podeu consultar les dades del vostre telèfon o utilitzar alguns telèfons com a pantalla en viu. Amb el dispositiu NodeMCU podeu registrar dades de temperatura i humitat fora , a l'habitació, hivernacle, laboratori, sala de refrigeració o qualsevol altre lloc completel

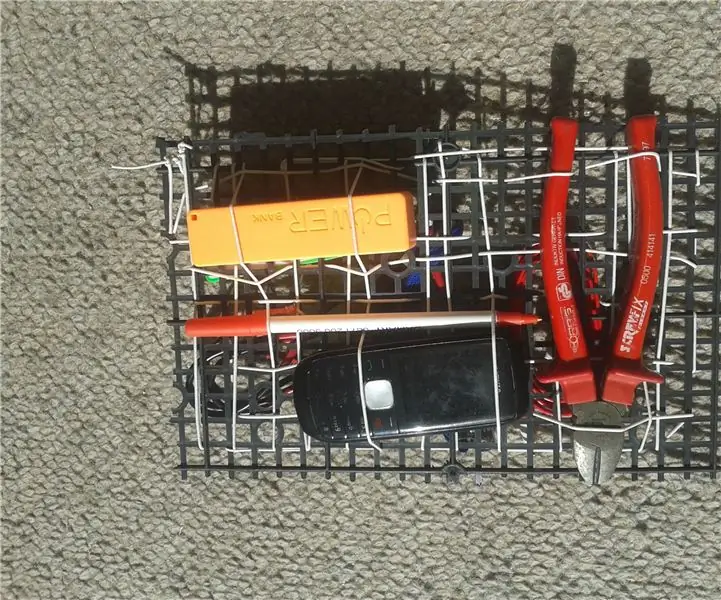

Tauler d'organitzador barat, de doble cara i d'estil quadrícula: 4 passos

Tauler d'organitzadors d'estil quadrícula barat, de doble cara: és una versió senzilla i econòmica dels organitzadors de quadrícula més brillants, forts i, en general, millors que podeu comprar. Em va costar fer una versió similar a l'original i vaig decidir que no valia la pena, però aquesta versió no costava precisament res (

Tauler de control de la nau espacial: joguina Arduino tallada amb làser: 11 passos (amb imatges)

Tauler de control de la nau espacial: joguina Arduino tallada amb làser: fa uns mesos vaig decidir formar part de l'espai local de fabricants, ja que des de feia anys que volia aprendre les eines del sector dels fabricants. Vaig tenir una petita experiència d’Arduino i havia pres un curs de Fusion aquí a Instructables. Tanmateix jo

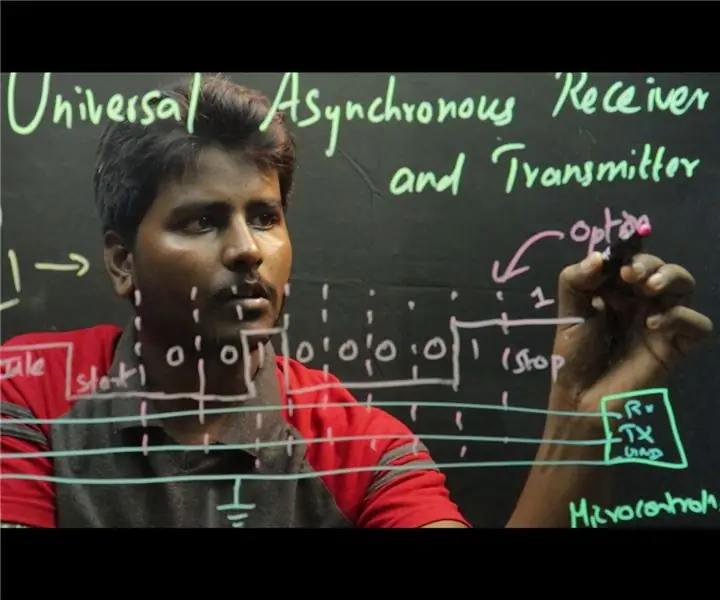

Tauler lleuger o tauler de vidre: 4 passos

DIY Lightboard o Glassboard: Hi ha moltes innovacions en el sector educatiu. L’ensenyament i l’aprenentatge a través d’Internet ja són coses quotidianes. La majoria de les vegades els tutors en línia tendeixen a centrar-se més en el contingut tècnic, deixant als espectadors desinteressats. Aprenentatge en 3D

UDuino: Tauler de desenvolupament compatible amb Arduino de molt baix cost: 7 passos (amb imatges)

UDuino: Taula de desenvolupament compatible amb Arduino de molt baix cost: les plaques Arduino són ideals per prototipar. No obstant això, són bastant cars quan teniu diversos projectes simultanis o necessiteu moltes plaques de control per a un projecte més gran. Hi ha algunes alternatives fantàstiques i econòmiques (Boarduino, Freeduino), però