Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:11.

- Última modificació 2025-01-23 14:37.

En aquest tutorial, escriurem el codi Verilog per controlar el servomotor. El servo SG-90 està fabricat per Waveshare. Quan compreu el servomotor, és possible que rebeu un full de dades que enumera la tensió de funcionament, el parell màxim i la modulació d’amplada de pols (PWM) proposada … etc. No obstant això, el FPGA DuePrologic proporciona una tensió d'entrada de 3,3V, on la tensió de funcionament del servo SG-90 és de 5V a 7V. A manca d’energia elèctrica, llistaré el meu PWM calibrat per tal de girar el servomotor amb èxit.

La nostra tasca: el servo motor gira endavant i endarrere amb el període de 5 segons

Menú complet:

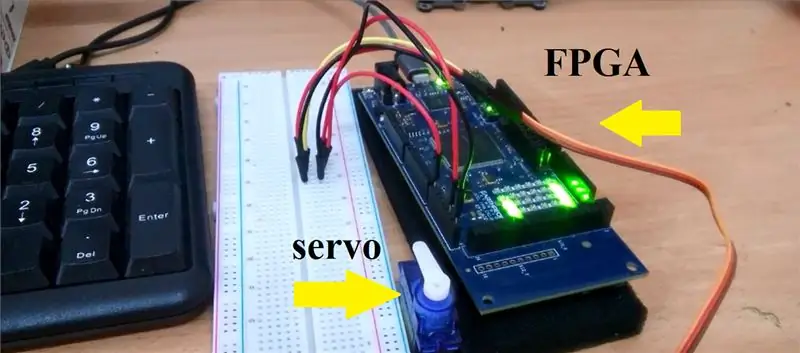

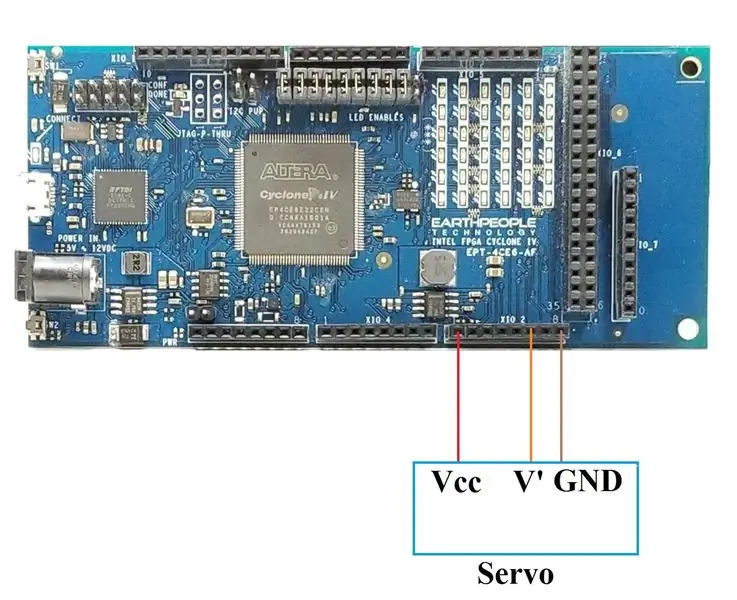

Pas 1: Construir un circuit electrònic

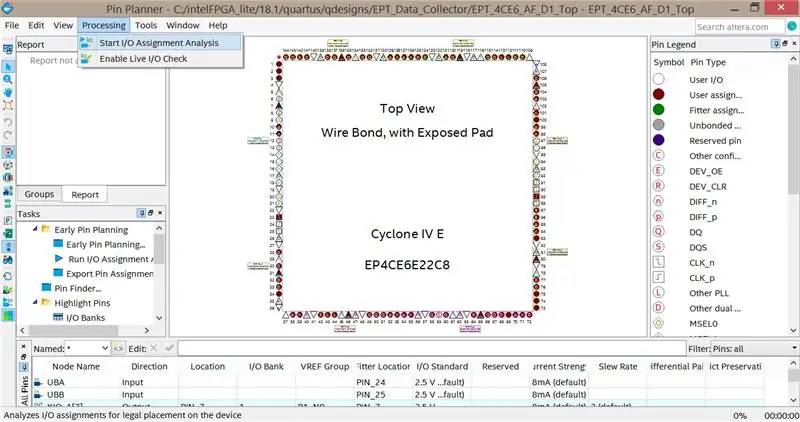

Pas 2: configureu el Planificador de pins

Feu clic a "Inicia l'anàlisi d'assignacions d'E / S" per comprovar si el planificador de pins està configurat correctament. En cas contrari, heu d’importar tots els noms dels ports.

Pas 3: codi de Verilog

Creem un temporitzador "servo_count". Quan "servo_A" és ALTA, el PWM fa 1,5 ms i, per tant, el servo es troba a 120 graus. En canvi, quan "servo_A" és BAIX, el PWM és de 0,15 ms i, per tant, el servo es manté a 0 graus.

assigna XIO_2 [3] = servo_pulse; // per a V '

reg [31: 0] servo_count;

inicial inicial

servo_count <= 32'b0;

servo_A <= 1'b0;

final

always @ (posedge CLK_66)

començar

servo_count <= servo_count + 1'b1;

if (servo_count> 400000000) // Cicle de rellotge a 66 MHz, 1/66 M * 400000000 ~ 5 segons

començar

servo_A <=! servo_A;

servo_count <= 32'b0;

final

final

reg [31: 0] ex_auto;

inicial inicial

ex_auto <= 32'b0;

servo_auto <= 1'b0;

final

always @ (posedge CLK_66)

començar

if (servo_A == 1'b1)

començar

ex_auto <= ex_auto + 1'b1;

si (ex_auto> 100000) // Cicle de rellotge a 66 MHz, aquest PWM fa ~ 1,5 ms, el servo gira a 120 graus

començar

servo_auto <=! servo_auto;

ex_auto <= 32'b0;

final

final

if (servo_A == 1'b0)

començar

ex_auto <= ex_auto + 1'b1;

si (ex_auto> 10000) // Cicle de rellotge a 66 MHz, aquest PWM fa ~ 0,15 ms, el servo gira a 0 graus

començar

servo_auto <=! servo_auto;

ex_auto <= 32'b0;

final

final

final

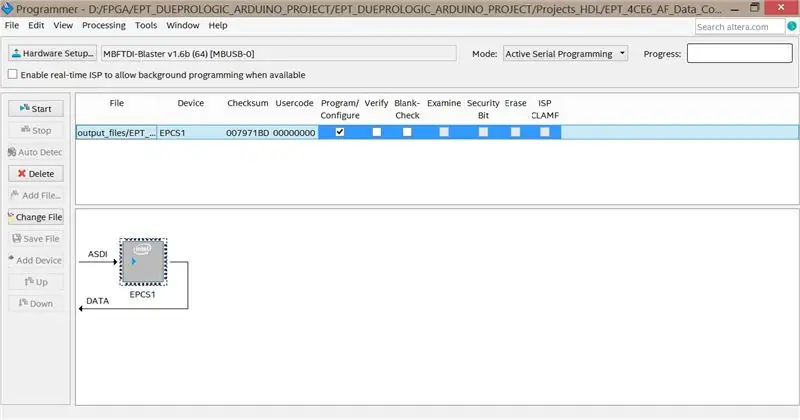

Pas 4: pengeu el codi de Verilog

Feu clic a "Inicia la compilació". Si no es mostra cap missatge d'error, aneu a "Programador" per completar la configuració del maquinari. Recordeu actualitzar el fitxer pof a "Canvia el fitxer" si cal. Feu clic a "Inici" per penjar el codi.

Al cap i a la fi, heu de veure que el servomotor gira periòdicament.

Recomanat:

FPGA Cyclone IV Controls DueProLogic Càmera Raspberry Pi: 5 passos

FPGA Cyclone IV Controls DueProLogic Controls Càmera Raspberry Pi: Tot i que el FPGA DueProLogic està dissenyat oficialment per a Arduino, farem que el FPGA i el Raspberry Pi 4B siguin comunicables. En aquest tutorial s’implementen tres tasques: (A) Premeu simultàniament els dos botons FPGA per capgirar l'angle de

FPGA Cyclone IV DueProLogic: polsador i LED: 5 passos

FPGA Cyclone IV DueProLogic - Pulsador i LED: en aquest tutorial, utilitzarem el FPGA per controlar el circuit LED extern. Implementarem les tasques següents (A) Utilitzeu els botons de control de FPGA Cyclone IV DuePrologic per controlar el LED. (B) LED de flaix a & desactivat periòdicament Laboratori de demostració de vídeo

Fitxer per lots: controls de moviment: 3 passos

Fitxer per lots: Controls de moviment: quan vaig buscar com crear controls de moviment a CMD no vaig trobar resultats precisos, així que vaig decidir fer els meus propis controls que funcionessin amb les tecles WASD per al moviment i les tecles 1234 per girar

Construint controls per a Makey Makey: 6 passos

Construint Controles Para Makey Makey: A construction of controles personalised for Makey Makey podem ser realitzats com a criança abans d’iniciar-se els jocs. A confecção is bem simples: 1) Faça um desenho o imprima uma imagem da internet (OBS: Você deve estar atento para a quantidade d

Redbear BLE Nano V2 Controls personalitzats amb PfodApp - No cal codificació: 6 passos

Redbear BLE Nano V2 Controls personalitzats amb PfodApp - No cal codificació: Actualització: 15 de setembre de 2017 - Aquest instructable s'ha actualitzat per utilitzar l'última versió de RedBear BLE Nano, V2. La versió anterior d’aquest instructiu, dirigida a RedBear BLE Nano V1.5, està disponible aquí. Actualització del 15 de novembre - 2017 Així doncs