Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:14.

- Última modificació 2025-01-23 14:38.

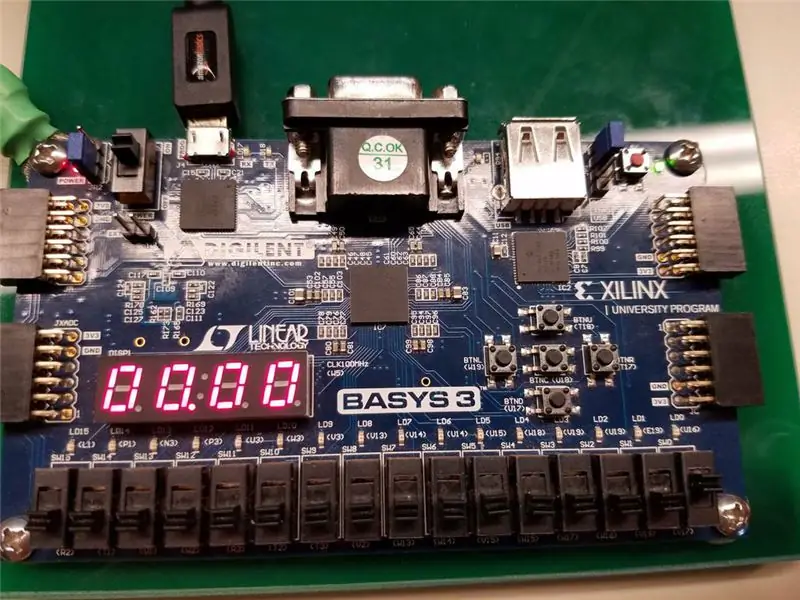

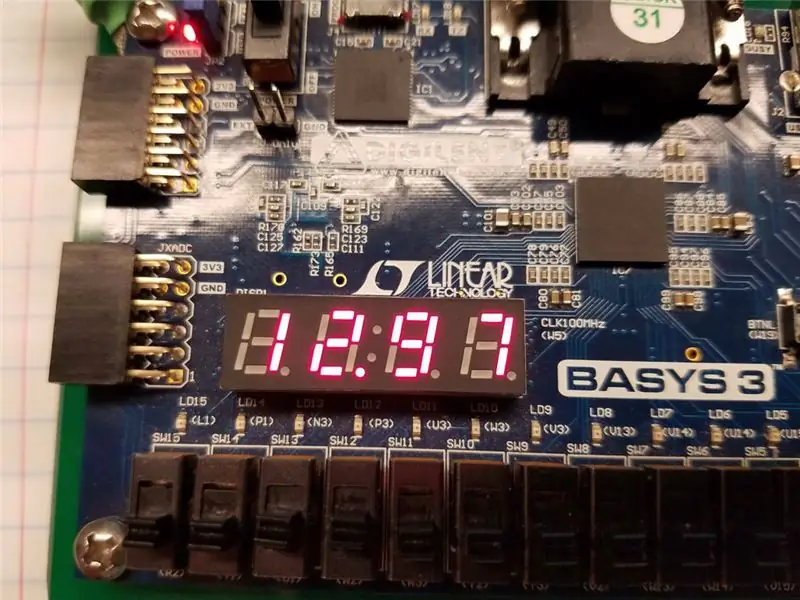

Benvingut a l'informable sobre com construir un cronòmetre mitjançant la placa bàsica VHDL i Basys 3. Estem encantats de compartir el vostre projecte amb vosaltres! Aquest va ser un projecte final del curs CPE 133 (Disseny digital) a Cal Poly, SLO a la tardor del 2016. El projecte que vam construir és un cronòmetre senzill que arrenca, restableix i posa en pausa el temps. Presa tres botons polsadors a la placa Basys3 com a entrades i l’hora es mostra a la pantalla de set segments de quatre dígits de la placa. El temps transcorregut es mostra en un format de segons: centisegons. Utilitza el rellotge del sistema del tauler com a entrada per fer un seguiment del temps transcorregut i transmet el temps als quatre dígits de la pantalla de set segments.

Pas 1: materials

Els materials que necessiteu per a aquest projecte:

- 1 ordinador amb Vivado Design Suite WebPack instal·lat des de Xilinx (preferiu la versió 2016.2)

- 1 placa Digilent Basys3 Xilinx Artix-7 FPGA

- 1 cable de port USB

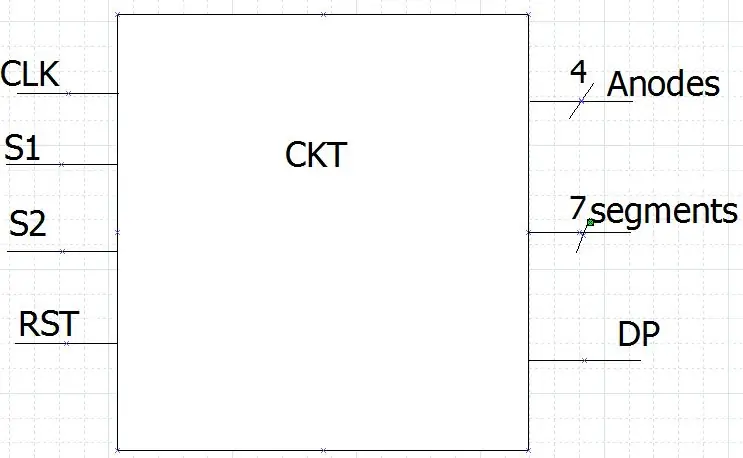

Pas 2: Configuració d'entrades i sortides

La figura anterior mostra un diagrama de blocs de nivell superior del mòdul de cronòmetre principal. El cronòmetre pren les entrades "CLK" (rellotge), "S1" (botó d'inici), "S2" (botó de pausa) i "RST" (restabliment) i té una sortida de 4 bits "Ànodes", un de 7 bits "segment" de sortida i una sortida "DP" d'un sol bit (punt decimal). Quan l'entrada "S1" és alta, el cronòmetre comença a comptar el temps. Quan "S2" és baix, el cronòmetre posa en pausa l'hora. Quan "RST" és alt, el cronòmetre s'atura i restableix l'hora. Hi ha quatre submòduls dins del circuit: el divisor de rellotge, el comptador de dígits, el controlador de pantalla de set segments i el codificador de pantalla de set segments. El mòdul principal del cronòmetre enllaça tots els submòduls i les entrades i sortides.

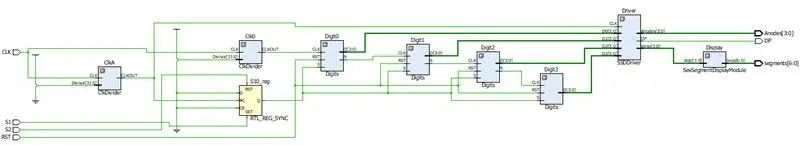

Pas 3: fabricació de rellotges

El mòdul divisor de rellotge pren un rellotge del sistema i utilitza una entrada divisora per crear un rellotge de qualsevol velocitat no superior a la del rellotge del sistema. El cronòmetre utilitza dos mòduls de rellotge diferents, un que crea un rellotge de 500 Hz i un altre que crea un rellotge de 100 Hz. L'esquema del divisor de rellotge es mostra a la figura anterior. El divisor de rellotge inclou una entrada de "bit CLK" d'un sol bit, i una entrada de 32 bits "Divisor" i la sortida d'un bit de bit "CLKOUT". "CLK" és el rellotge del sistema i "CLKOUT" és el rellotge resultant. El mòdul també inclou una porta NOT, que commuta el senyal "CLKTOG" quan el recompte arriba al valor del divisor.

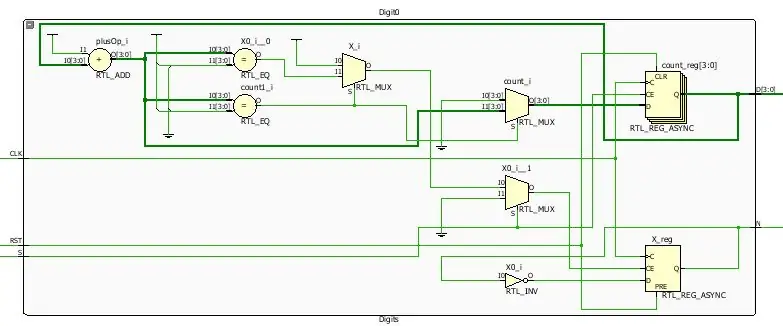

Pas 4: Compte fins a deu

El comptador de dígits compta cada dígit del 0 al 10 i crea un altre rellotge per al següent dígit que funcioni fora que oscil·la quan el recompte arriba a 10. El mòdul inclou 3 entrades d'un sol bit "S", "RST" i "CLK "i dóna com a resultat una sortida de" bit "d'un sol bit i una sortida de" D "de 4 bits. L'entrada "S" és l'habilitació de l'entrada. El rellotge s'activa quan "S" és alt i s'apaga quan "S" és baix. "RST" és l'entrada de restabliment, de manera que el rellotge es reinicia quan "RST" és alt. "CLK" és l'entrada de rellotge del comptador de dígits. "N" és la sortida del rellotge que es converteix en el rellotge d'entrada del següent dígit. La sortida "D" presenta el valor binari del dígit en què es troba el comptador.

Pas 5: mostrar números

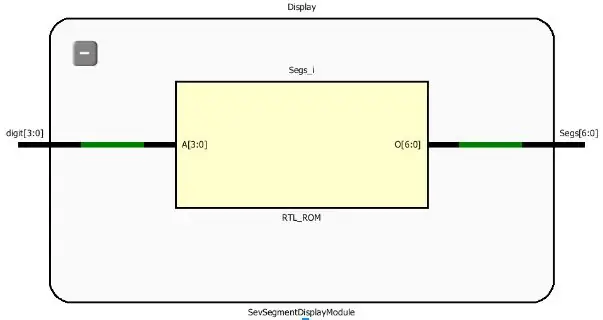

El codificador de pantalla de set segments codificarà el número binari rebut del mòdul del controlador de pantalla de set segments i el convertirà en un flux de bits que s’interpretaran com a valors “1” o “0” per a cada segment de la pantalla. El mòdul rep el número binari com a "dígit" d'entrada de 4 bits i dóna lloc als "segments" de sortida de 7 bits. El mòdul consta d’un bloc de procés de majúscules i minúscules que assigna un flux de 7 bits específic per a cada valor d’entrada possible de 0 a 9. Cada bit dels fluxos de set bits representa un dels set segments dels dígits de la pantalla. L'ordre dels segments del tauler d'activitat és "abcdefg" i el "0" representa els segments que s'encenen per al nombre donat.

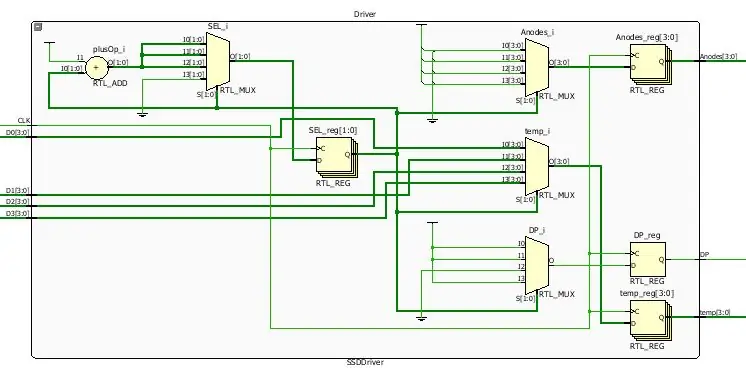

Pas 6: Com es mostra el cronòmetre

Al mòdul del controlador de pantalla de set segments, hi ha quatre entrades de 4 bits "D0", "D1", "D2" i "D3", que representen cadascun els quatre dígits que es mostraran. L'entrada "CLK" és l'entrada de rellotge del sistema. La sortida d'un bit "DP" representa el punt decimal a la pantalla de set segments. La sortida de 4 bits "Ànodes" determina quin dígit de la pantalla de set segments es mostra i la sortida de 4 bits "temp" depèn de l'estat de l'entrada de control de 2 bits "SEL". El mòdul utilitza 4 multiplexors per a l'entrada de control "SEL" i les tres sortides; "Ànodes", "temp" i "DP".

Pas 7: Unir-ho tot

Per crear els botons d’inici i pausa s’utilitza un bloc de procés “si” que s’executa al rellotge de 500Hz. A continuació, enllaceu tots els submòduls al mòdul principal del cronòmetre declarant els components de cada submòdul individual i utilitzant diversos senyals. Els submòduls de dígits prenen la sortida del rellotge del submòdul de dígits anterior i el primer pren el rellotge de 100Hz. Les sortides "D" dels submòduls de dígits es converteixen en les entrades "D" del mòdul de control de visualització de set segments. I, finalment, la sortida "temporal" del mòdul del controlador de pantalla de set segments es converteix en l'entrada "temporal" del mòdul codificador de set segments.

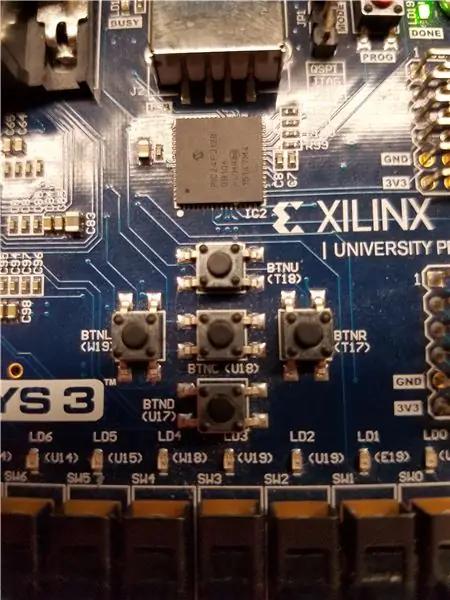

Pas 8: restriccions

Utilitzeu 3 polsadors (W19, T17 i U18) per a les entrades "RST", "S1" i "S2". W19 és el botó de restabliment, T17 és el botó d’inici (S1) i U18 és el botó de pausa (S2). També es requereix una restricció per a l'entrada d'entrada de rellotge mitjançant el port W5. A més, recordeu afegir aquesta línia a la restricció del rellotge:

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {CLK}]

També enllaceu els ànodes i els segments amb el tauler perquè el cronòmetre es mostri a la pantalla de set segments tal com es veu al fitxer de restriccions.

Pas 9: proves

Assegureu-vos que el dispositiu funcioni jugant amb els tres botons: premeu-los i manteniu-los premuts en tot ordre possible per trobar possibles problemes amb el vostre codi.

Recomanat:

Cronòmetre de Croakers: 16 passos (amb imatges)

Cronòmetre de Croakers: si somriu a les granotes, algunes d'elles vibraran. En entendre el moviment, es pot dir el temps: una operació inestable. Granotes " mirant cap amunt " representar les hores en binari (d’esquerra a dreta; 8,4,2,1). Ranes " mirant cap endavant " representa min

Cronometre digital tot en un (rellotge, temporitzador, alarma, temperatura): 10 passos (amb imatges)

Cronometre digital Tot en Un (Rellotge, Temporitzador, Alarma, Temperatura): Teníem previst fer un Temporitzador per a una altra competició, però més tard també vam implementar un rellotge (sense RTC). A mesura que vam entrar a la programació, ens vam interessar per aplicar més funcionalitats al dispositiu i vam acabar afegint DS3231 RTC, com

Com fer un cronòmetre amb Arduino: 8 passos (amb imatges)

Com fer un cronòmetre amb Arduino: es tracta d’un cronòmetre de pantalla LCD Arduino de 16 * 2 molt senzill ……….. Si us agrada aquest instructiu, subscriviu-vos al meu canal https://www.youtube.com / ZenoModiff

Cronòmetre VHDL d'un minut: 5 passos

Cronòmetre d’un minut VHDL: es tracta d’un tutorial sobre com construir un cronòmetre d’un minut mitjançant VHDL i una placa Basys 3. Aquest dispositiu és ideal per a jocs on cada jugador té un màxim d’un minut per fer el seu moviment. El cronòmetre mostra amb precisió segons i mil·lisegons o

Cronòmetre VHDL: 8 passos (amb imatges)

Cronòmetre VHDL: es tracta d’un tutorial sobre com fer un cronòmetre amb VHDL i una placa de circuit FPGA, com una placa Basys3 Atrix-7. El cronòmetre pot comptar de 00.00 segons a 99.99 segons. Utilitza dos botons, un per al botó d'inici / atura i un altre per al botó