Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:16.

- Última modificació 2025-01-23 14:38.

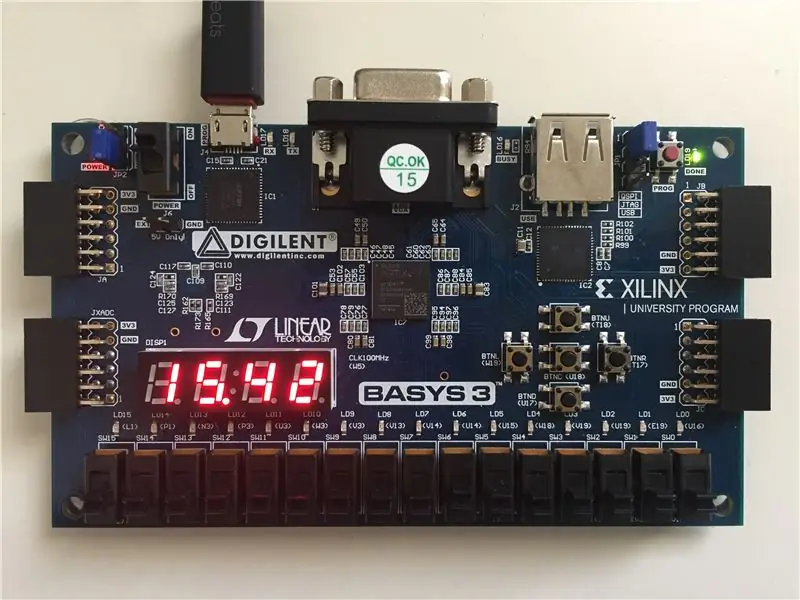

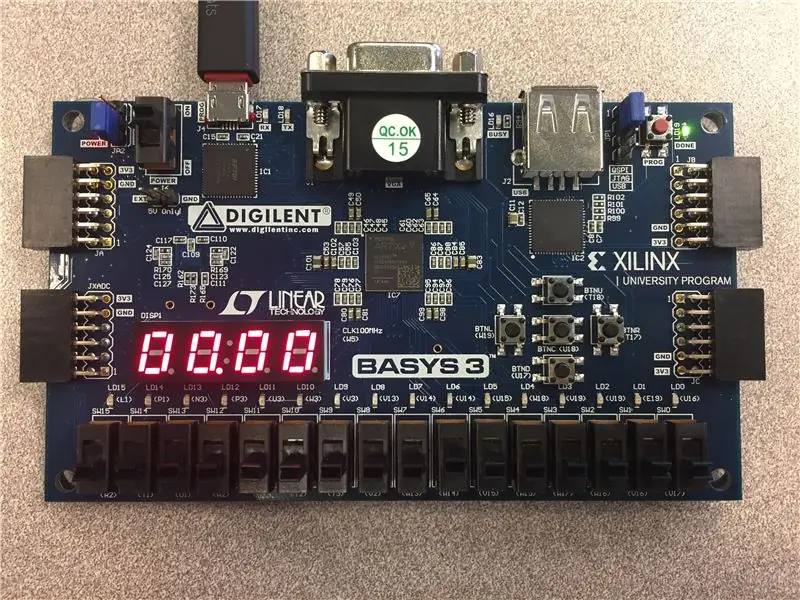

Aquest és un tutorial sobre com fer un cronòmetre amb VHDL i una placa de circuit FPGA, com una placa Basys3 Atrix-7. El cronòmetre pot comptar de 00.00 segons a 99.99 segons. Utilitza dos botons, un per al botó d'inici / aturada i un altre per al botó de reinici. Els números es mostren a la pantalla de set segments del tauler mitjançant els seus ànodes i càtodes. Hi ha tres fitxers diferents necessaris per fer funcionar aquest cronòmetre.

Pas 1: maquinari / programari

- Basys3 Atrix-7 FPGA Board

- Vivado Design Suite de Xilinx

- USB 2.0 A mascle a micro-B mascle

Pas 2: diagrama de blocs

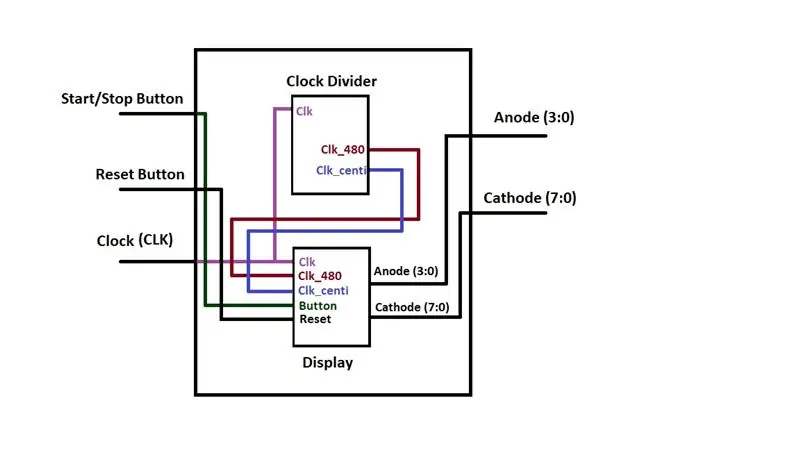

El cronòmetre general té tres entrades i dues sortides. Les tres entrades són l'inici / aturada, el reinici i el rellotge. L’inici / parada i el restabliment són botons i el rellotge és el rellotge de 100 MHz de la placa. Les dues sortides són els ànodes i els càtodes per a la visualització de set segments.

El primer mòdul (divisor de rellotge) té una entrada i dues sortides. L’entrada és el rellotge de 100 MHz de la placa i les sortides són dos rellotges separats, un de 480Hz i un altre de 0,5MHz.

El segon mòdul (pantalla) té cinc entrades i dues sortides. Les entrades són el rellotge de 100 MHz de la placa, els dos rellotges del mòdul divisor de rellotge i els botons d’inici / parada i reinici. Les sortides són els ànodes i els càtodes.

L'últim mòdul (modelat per tot el diagrama de blocs) té tres entrades i dues sortides. Aquest és el fitxer que ho reuneix tot. Les entrades són els 100 MHz de la placa i els botons d’inici / parada i reinici. Les sortides són els ànodes i els càtodes que controlen la pantalla de set segments. Totes les entrades i sortides es troben físicament a la placa del mòdul final.

Pas 3: diagrama d'estats

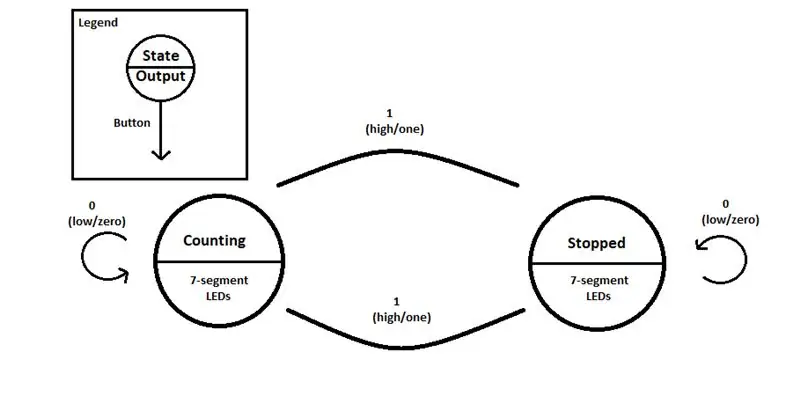

La imatge superior mostra el diagrama d’estat del funcionament del cronòmetre. Si premeu el botó de restabliment, no afectarà l'estat del cronòmetre. El següent estat el determina el botó d'inici / aturada. L'inici / parada és "HIGH" quan es prem, però no quan es manté premut, i "LOW" quan el botó ha rebotat o s'ha mantingut premut després d'haver estat "HIGH" momentàniament.

Si el cronòmetre compta i el botó d'inici / parada passa a "ALT", deixarà de comptar. Si el cronòmetre està aturat i el botó d'inici / aturat es posa "ALT", torna a començar a comptar. Per als dos estats, si el botó d'inici / aturada és "BAIX", es mantindrà a l'estat en què es troba actualment.

Pas 4: mòdul divisor de rellotge

El mòdul divisor de rellotge té una entrada, el rellotge de 100 MHz de la placa i dues sortides, els de 480Hz i els de 0,5MHz. El rellotge de 480Hz s’utilitza per mantenir tots els LEDs de la pantalla de set segments “encesos” al mateix temps canviant ràpidament els quatre. El rellotge de 0,5 MHz s’utilitza perquè el cronòmetre compti realment en centi-segons.

Pas 5: visualitzeu el mòdul

Aquest mòdul de visualització té cinc entrades, el rellotge de 100 MHz de la placa, els dos rellotges del mòdul de rellotge, i els botons d’inici / parada i reinici, i dues sortides, els ànodes i els càtodes. Aquest mòdul també té la "lògica" de com compta el cronòmetre i incorpora la màquina d'estats finits.

Pas 6: mòdul d'enquadernació

Aquest mòdul final és el que uneix els altres dos mòduls. Té tres entrades, el rellotge de 100 MHz de la placa i els botons d’inici / parada i reinici, i dues sortides, els ànodes i els càtodes. El rellotge de 100 MHz passa al mòdul divisor de rellotge i al mòdul de visualització, i els botons d’inici / atura i reinici van al mòdul de visualització. Les sortides del mòdul divisor de rellotge (480Hz i 0,5MHz) van a les dues entrades de rellotge del mòdul de visualització. Les sortides del mòdul de visualització (ànodes i càtodes) van a les sortides del mòdul final.

Pas 7: restriccions

Les dues entrades poden ser qualsevol botó de la placa Basys3 Atrix-7 FPGA i les sortides seran els quatre ànodes i els vuit càtodes (perquè també voleu un punt decimal entre segons i mil·lisegons) per a la visualització de set segments.

Pas 8: Fet

Carregueu el programa a la vostra placa FPGA Basys3 Atrix-7 i premeu el botó d'inici / aturada per engegar el cronòmetre.

Recomanat:

Cronòmetre de Croakers: 16 passos (amb imatges)

Cronòmetre de Croakers: si somriu a les granotes, algunes d'elles vibraran. En entendre el moviment, es pot dir el temps: una operació inestable. Granotes " mirant cap amunt " representar les hores en binari (d’esquerra a dreta; 8,4,2,1). Ranes " mirant cap endavant " representa min

Cronometre digital tot en un (rellotge, temporitzador, alarma, temperatura): 10 passos (amb imatges)

Cronometre digital Tot en Un (Rellotge, Temporitzador, Alarma, Temperatura): Teníem previst fer un Temporitzador per a una altra competició, però més tard també vam implementar un rellotge (sense RTC). A mesura que vam entrar a la programació, ens vam interessar per aplicar més funcionalitats al dispositiu i vam acabar afegint DS3231 RTC, com

Com fer un cronòmetre amb Arduino: 8 passos (amb imatges)

Com fer un cronòmetre amb Arduino: es tracta d’un cronòmetre de pantalla LCD Arduino de 16 * 2 molt senzill ……….. Si us agrada aquest instructiu, subscriviu-vos al meu canal https://www.youtube.com / ZenoModiff

Cronòmetre bàsic amb VHDL i Basys3 Board: 9 passos

Cronòmetre bàsic amb la placa VHDL i Basys3: us donem la benvinguda a la informació sobre com construir un cronòmetre mitjançant la placa bàsica VHDL i Basys 3. Estem encantats de compartir el vostre projecte amb vosaltres! Aquest va ser un projecte final del curs CPE 133 (Disseny digital) a Cal Poly, SLO a la tardor del 2016. El projecte que vam construir

Cronòmetre VHDL d'un minut: 5 passos

Cronòmetre d’un minut VHDL: es tracta d’un tutorial sobre com construir un cronòmetre d’un minut mitjançant VHDL i una placa Basys 3. Aquest dispositiu és ideal per a jocs on cada jugador té un màxim d’un minut per fer el seu moviment. El cronòmetre mostra amb precisió segons i mil·lisegons o