Taula de continguts:

- Pas 1: Configuració d'un projecte a Vivado per a Ernie

- Pas 2: Creació del PWM d'Ernie a Vivado

- Pas 3: Creació del TDOA d'Ernie a Vivado

- Pas 4: embolicar i exportar Ernie

- Pas 5: Construir Ernie

- Pas 6: primer BSP d'Ernie

- Pas 7: Ernie de FreeRTOS

- Pas 8: importació del codi C d'Ernie

- Pas 9: depurar Ernie

- Pas 10: Fer que Ernie sigui autònom

- Pas 11: fer que l'Ernie sigui bonic

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:11.

- Última modificació 2025-01-23 14:37.

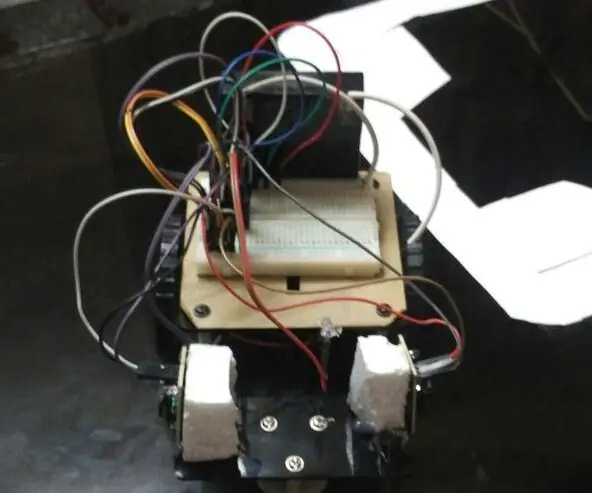

Aquest és un tutorial sobre com construir Ernie, el vostre robot autònom de seguiment de so, mitjançant una placa Zybo. Es tractarà de com crear un projecte a Vivado, crear servomotors de tipus PWM a l’FPGA, interfície amb dos sensors de so, crear una diferència horària d’IP d’arribada, utilitzar freeRTOS i executar el zybo amb una bateria. Aquest va ser el nostre projecte final per a una classe de sistemes operatius en temps real (CPE 439) a Cal Poly SLO.

Llista d'equips:

- 1 - Tauler de desenvolupament ZYBO Zynq 7000

- 2 - Servo de rotació contínua Parallax

- 2 - Sensor de so (Detector de so SparkFun)

- Paquet de bateries USB d'ió de liti de 5 a 5 v (per a placa)

- 4 - piles AA (per servos)

- 1 - bateria AA (amb 4 ranures per a bateria)

- 1 - Cable micro USB

- 1 - Taula de pa

- molts: cables masculins a masculins

- 1 - Servo xassís

Requisits de programari:

- Xilinx Vivado Design Suite 2016.2

- Digilent Adept 2.16.1

Pas 1: Configuració d'un projecte a Vivado per a Ernie

- Apareixerà un assistent

- Feu clic a Següent

-

El nom següent del projecte

- No utilitzeu mai un nom de projecte ni una ruta de directori que tingui espais !!!!!

- Aquest serà un projecte RTL.

- No volem especificar fonts

-

Fent clic a Següent, arribem a la pàgina Part. Estem utilitzant un ZYNQ XC7Z010-1CLG400C.

- Vivado no té el Zybo llistat com un dels taulers predefinits. Seleccioneu: "parts" i cerqueu xc7z010clg400-1.

- Si escolliu la part equivocada per error, podeu canviar de fitxa fàcilment: Eines -> Configuració del projecte -> General i feu clic als punts a la dreta de "Dispositiu del projecte".

-

Feu clic a Crea disseny de blocs.

Posa-li nom design_1 ara per ara

- Veureu una barra verda que diu Afegeix IP, feu-hi clic.

-

Cerca de Zynq.

- Feu doble clic a Sistema de processament ZYNQ7,

- Aquest bloc apareixerà al nostre disseny de blocs.

- Veureu una barra verda que diu Run Block Automation, feu-hi clic.

- Baixeu zybo_zynq_def.xml a continuació.

-

A Vivado, feu clic a "Importa la configuració de XPS" i seleccioneu "zybo_zynq_def.xml"

Això preemplena la configuració del bloc Vivado amb tots els perifèrics i assignacions de pins incorporats de la placa Zybo

-

Feu doble clic al bloc ZYNQ.

-

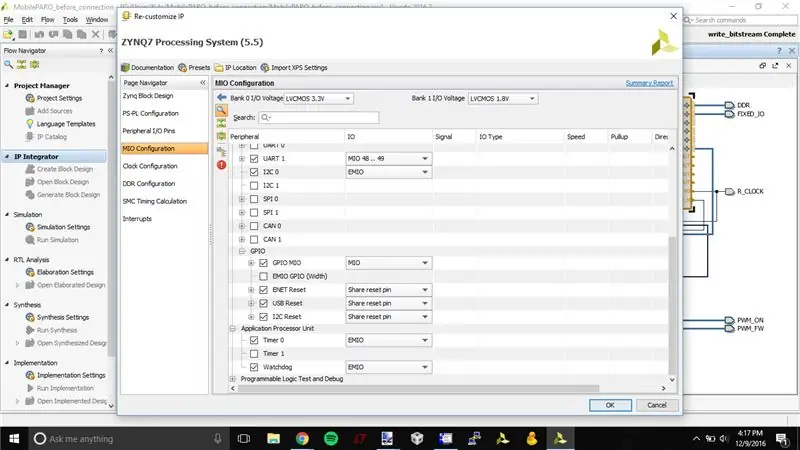

Configuració MIO

- Activa el temporitzador 0 (a Unitat de processador d'aplicacions - img 1)

- Activa Watchdog (a la Unitat de processador d'aplicacions - img 1)

- Activa GPIO-> GPIO MIO (a la Unitat de processador d'aplicacions - img 2)

- Activa GPIO-> Restabliment ENET (a la secció Perifèrics d'E / S- img 2)

-

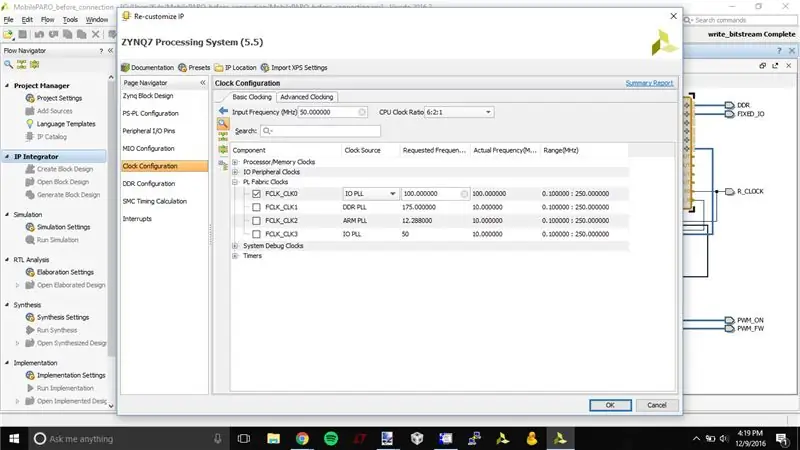

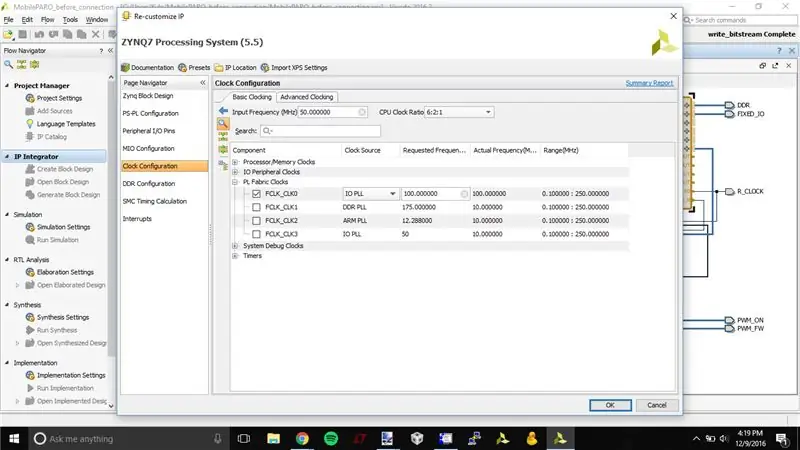

Configuració del rellotge

Desactiva FCLK0 (a sota de Rellotges de tela PL - img 3)

-

- Feu clic a D'acord.

-

"Executeu l'automatització de blocs" ara.

Hi haurà algunes preguntes sobre els senyals, diguem OK

-

Feu clic a "Genera embolcall HDL".

Voldrem copiar l’embolcall generat per permetre les modificacions dels usuaris

- Feu clic a D'acord.

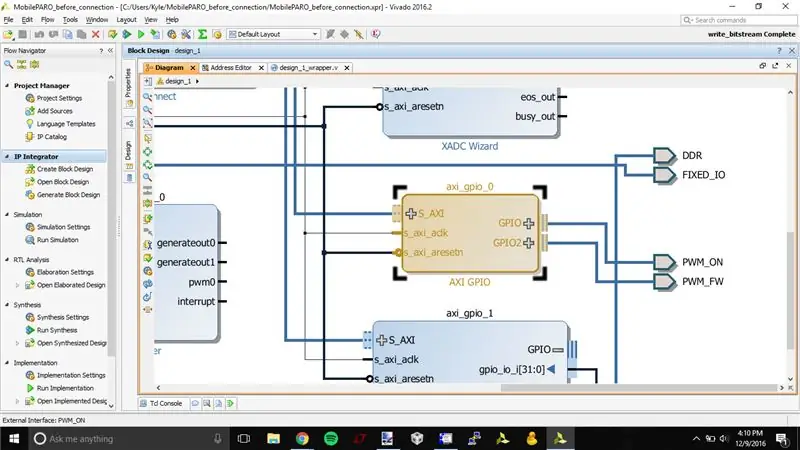

Pas 2: Creació del PWM d'Ernie a Vivado

Aquest pas generarà una IP PWM amb entrades enviades a través de la biblioteca AXI.

-

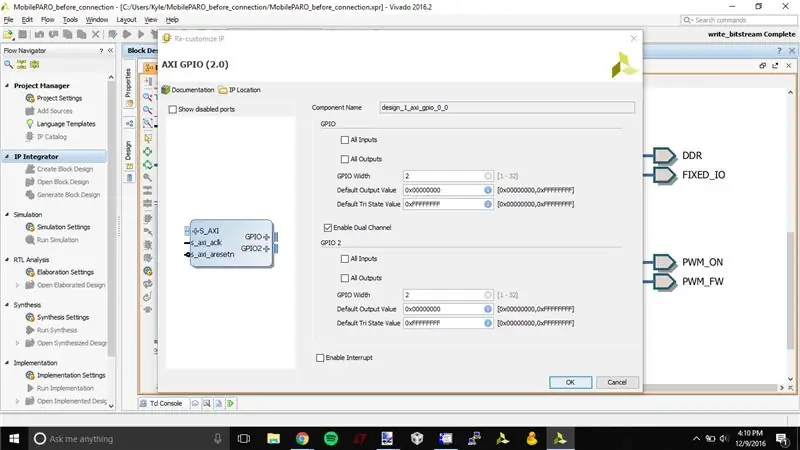

Per crear el bloc AXI GPIO, feu clic amb el botó dret al fons i feu clic a "Afegeix IP"

escriviu "AXI_GPIO" a la barra de cerca i seleccioneu aquest paquet

-

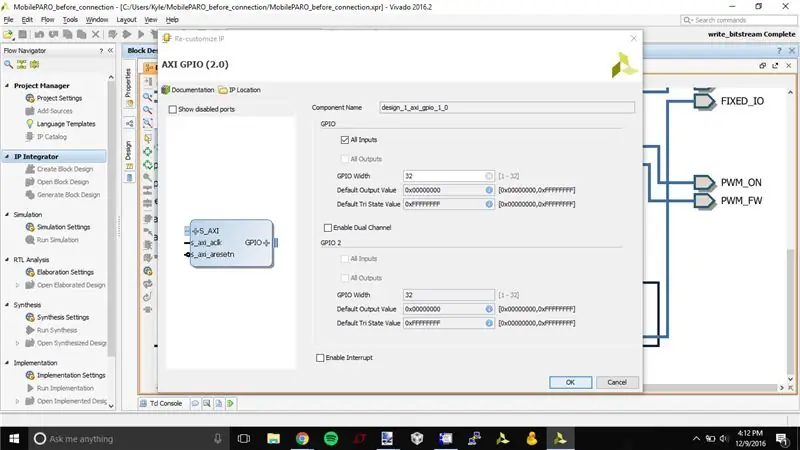

Torneu a personalitzar la IP fent doble clic al nou bloc axi_gpio_0

- a GPIO, configureu l'amplada GPIO a 2. Aquests bits seran el senyal PWM_ON per conduir cada instància del mòdul PWM.

- feu clic a "habilitar doble canal"

- a GPIO 2, configureu l'amplada GPIO a 2. Aquests bits seran el senyal PWM_FW per establir la direcció de cada instància del mòdul PWM.

-

Feu clic amb el botó dret al port de sortida axi_gpio_0 amb l'etiqueta GPIO i seleccioneu "Fes extern"

- Feu clic a la nova sortida etiquetada amb GPIO i aneu a la pestanya "propietats" de la barra d'eines esquerra i canvieu el nom a PWM_ON

- Feu clic a la nova sortida etiquetada amb GPIO2 i aneu a la pestanya "propietats" de la barra d'eines esquerra i canvieu el nom a PWM_FW

-

Seleccioneu Executa l'automatització de la connexió al bàner verd que hi ha a sobre del diagrama de blocs.

Si connecteu manualment els ports, és possible que les adreces AXI no es configurin, cosa que provocarà problemes de comunicació més endavant

-

Al panell del navegador de flux, seleccioneu gestor de projectes -> Afegeix fonts per crear un nou bloc IP personalitzat

- trieu "afegir o crear fonts de disseny" i premeu següent

- feu clic a "crear fitxer", canvieu el tipus de fitxer a "SystemVerilog" i escriviu "pwm" al camp del nom del fitxer i feu clic a D'acord

- feu clic a Finalitza

-

ignoreu la finestra Define Module (Premeu OK) (les sobreescriurem més endavant)

si us pregunta si esteu segur, feu clic a Sí

-

A la pestanya Fonts, feu doble clic a pwm.sv (situat a "Fonts de disseny / design_1_wrapper")

Copieu / enganxeu tot el codi SystemVerilog del fitxer pwm.txt adjunt a continuació

Pas 3: Creació del TDOA d'Ernie a Vivado

Aquest pas generarà una IP TDOA la sortida de la qual es pot llegir a través de la biblioteca AXI

-

Per crear el bloc AXI GPIO, feu clic amb el botó dret al fons i feu clic a "Afegeix IP"

escriviu "AXI_GPIO" a la barra de cerca i seleccioneu aquest paquet

-

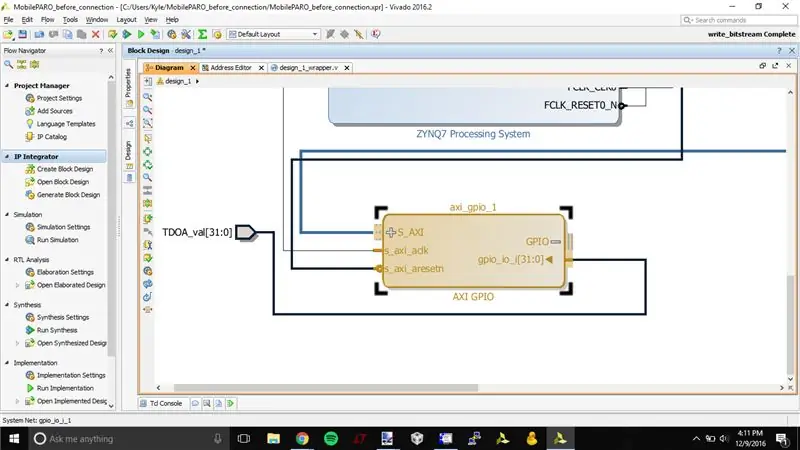

Torneu a personalitzar la IP fent doble clic al nou bloc axi_gpio_1

- a GPIO, marqueu la casella "Totes les entrades" i configureu l'amplada GPIO a 32. Aquest bus serà la diferència horària d'arribada entre els dos sensors.

- dins del bloc axi_gpio_1, feu clic al + situat al costat del port GPIO per mostrar gpio_io_i [31: 0].

-

Feu clic amb el botó dret al port de sortida axi_gpio_1 amb l'etiqueta gpio_io_i [31: 0] i seleccioneu "Fes extern"

Feu clic a l'entrada nova anomenada gpio_io_i [31: 0] i aneu a la pestanya "propietats" de la barra d'eines de l'esquerra i canvieu el nom a TDOA_val

-

Seleccioneu Executa l'automatització de la connexió al bàner verd que hi ha a sobre del diagrama de blocs.

Si connecteu manualment els ports, és possible que les adreces AXI no es configurin, cosa que provocarà problemes de comunicació més endavant

-

Al tauler del navegador de flux, seleccioneu gestor de projectes -> Afegeix fonts per crear un nou bloc IP personalitzat

- trieu "afegir o crear fonts de disseny" i premeu següent

- feu clic a "crear fitxer", canvieu el tipus de fitxer a "SystemVerilog" i escriviu "tdoa" al camp del nom del fitxer i feu clic a D'acord

- feu clic a Finalitza

-

ignoreu la finestra Define Module (Premeu OK) (les sobreescriurem més endavant)

si us pregunta si esteu segur, feu clic a Sí

-

A la pestanya Fonts, feu doble clic a tdoa.sv (situat a "Fonts de disseny / design_1_wrapper")

Copieu / enganxeu tot el codi SystemVerilog del fitxer tdoa.txt adjunt a continuació

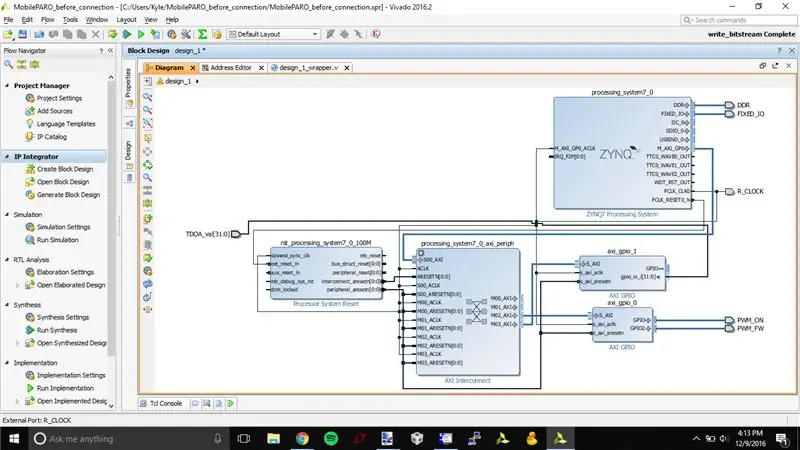

Pas 4: embolicar i exportar Ernie

- Verifiqueu que el diagrama de blocs sembli la captura de pantalla adjunta

-

A la pestanya Fonts, feu clic amb el botó dret a design_1.bd i seleccioneu "Crea HDL Wrapper …"

- Seleccioneu "Copia la sortida generada per permetre les modificacions de l'usuari" i premeu "D'acord"

- Copieu el codi de design_1_wrapper.txt adjunt a continuació i enganxeu-lo en lloc del codi generat de design_1_wrapper.v

- deseu design_1_wrapper.v

-

A la pestanya Fonts, feu doble clic al fitxer ZYBO_Master.xdc a Constraints / constrs1

- Copieu el codi de ZYBO_Master.txt adjunt a continuació i enganxeu-lo en lloc del codi ZYBO_Master.xdc existent

-

Tingueu en compte els següents pins d'entrada / sortida:

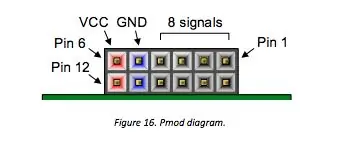

- L15: senyal PWM per al motor esquerre (Pmod JA2 al Zybo)

- L14: senyal PWM per al motor correcte (Pmod JA8 al Zybo)

- V12: entrada de porta del sensor de so 1 (Pmod JE1 al Zybo)

- K16: entrada de porta del sensor de so 2 (Pmod JE2 al Zybo)

- Al tauler del navegador de flux, feu clic a "Genera flux de bits" a Programa i depura

si creieu que es fa de seguida, probablement no. de debò, feu una mica de te

-

Feu clic a Fitxer-> Exporta-> Genera maquinari

Marqueu "Inclou Bitstream" i premeu D'acord

- Feu clic a Fitxer-> Inicia l'SDK

Pas 5: Construir Ernie

- Munteu els servos al xassís del servo.

-

Seguint el full de dades dels servos, feu el següent:

- connecteu la terra dels servos als pins de terra del JA Pmod de Zybo (veure imatge adjunta)

- connecteu el pin d'alimentació dels servos a la bateria AA

Hem trobat que quan els servos estan connectats a la Vdd de Zybo, la placa consumeix massa corrent, cosa que provoca que la placa es restableixi contínuament

- connecteu els pins de senyal d’entrada als pins de sortida adequats de Zybo (esquerra: JA2, dreta: JA8)

- munteu els sensors de so a la part frontal del xassís, mirant cap endavant, mantenint-los el més a prop possible

-

utilitzeu la guia de connexió del sensor de so per integrar els sensors de so

- connecteu els pins de terra i Vdd de cada sensor de so a terra i els pins Vdd del JE Pmod de Zybo (vegeu la imatge adjunta)

- connecteu el pin Gate del sensor de so esquerre a JE1

- connecteu el pin Gate del sensor de so adequat a JE2

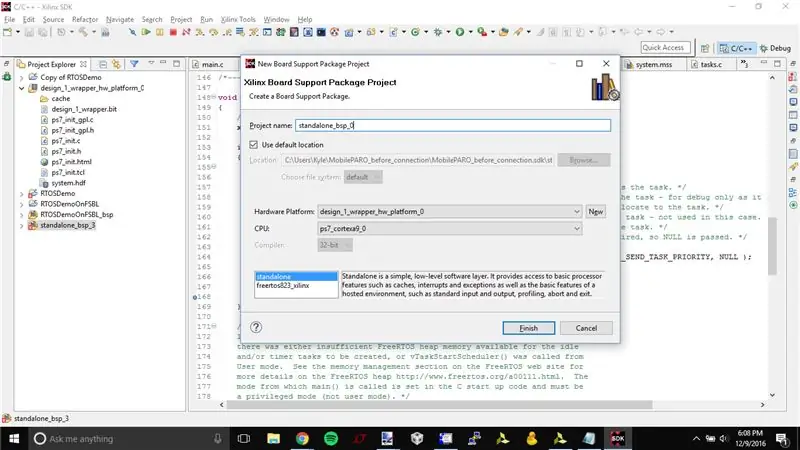

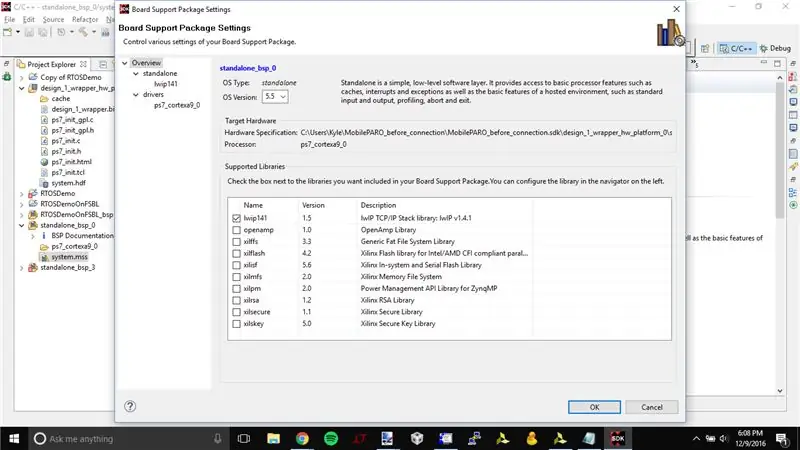

Pas 6: primer BSP d'Ernie

-

Creeu un BSP per acabar la plataforma que acabem de crear.

Podeu obtenir-ho mitjançant Fitxer -> Nou -> Paquet de suport al tauler

-

Apareixerà un assistent per ajudar-vos a crear el BSP.

- Volem vincular aquest BSP amb la nostra plataforma que acabem de crear, per tant

- La plataforma de maquinari hauria d’estar alineada amb la que acabem de crear (vegeu la imatge 1)

- La nostra CPU serà la CPU _0.

- Feu clic a Finalitza

- Assegureu-vos de marcar lwip141 per incloure-ho amb el vostre bsp a la finestra que apareix (vegeu la imatge 2)

Pas 7: Ernie de FreeRTOS

-

Descarregueu la versió més recent de FreeRTOS des de Sourceforge.

Si la descàrrega és executable, executeu-la per extreure els fitxers FreeRTOS al directori del projecte

- Mantingueu l'SDK obert i feu clic a Fitxer -> Importa.

- Volem fer clic a General-> Des d’un espai de treball existent i, a continuació, voldrem navegar fins on hem descarregat FreeRTOS.

-

La nostra demostració es troba a FreeRTOS / Demo / CORTEX_A9_Zynq_ZC702. En seleccionar aquesta carpeta, hauríem de veure aparèixer tres projectes (el nostre codi (SO), és BSP i la plataforma HW).

NOMÉS Importeu RTOSDemo al vostre espai de treball actual

-

En tots els projectes de carpeta "blava", canvieu el BSP referenciat

- Feu clic amb el botó dret i seleccioneu "Canvia el BSP referenciat".

- Seleccioneu el BSP que acabeu de crear per al vostre Zybo

- L’edició de codi a les carpetes blaves de l’SDK de Xilinx són els projectes de codi reals.

Pas 8: importació del codi C d'Ernie

- Al directori RTOSDemo / src, sobreescriviu el main.c existent amb el fitxer main.c adjunt aquí.

- Copieu el fitxer main_sound.c al directori RTOSDemo / src.

Pas 9: depurar Ernie

- Seleccioneu Executa -> Configuracions de depuració

- Al tauler esquerre, creeu una nova execució del depurador del sistema

-

A la pestanya Configuració de destinació,

seleccioneu "Restableix tot el sistema" de manera que estiguin seleccionats tant that com ps7_init

-

Ara seleccioneu la pestanya Aplicació.

- Seleccioneu "descarregar l'aplicació"

- Estableix el nucli cortexa9_0 a "atura't a l'entrada del programa"

- Feu clic a Aplica i depura.

- Verifiqueu que no hi hagi errors en el procés de depuració

- Vigilant bé el robot, premeu el botó Reprèn fins que el programa s’executi sense tocar cap punt d’interrupció

- Ara el robot hauria de girar i avançar cap a sorolls forts. Visca!

Pas 10: Fer que Ernie sigui autònom

- Un cop el vostre projecte estigui a punt (podeu executar-lo sense problemes a través del depurador), el podreu carregar a la memòria flash de la vostra placa.

-

Creeu el que s'anomena el projecte "carregador d'arrencada de primera fase" (FSBL) i conté totes les instruccions que necessitarà la vostra placa per carregar els fitxers del projecte (el flux de bits i el SO) a l'inici.

- Seleccioneu: Fitxer-> Nou-> Projecte d'aplicació i apareixerà la finestra següent.

- Posa-li el nom que vulguis (és a dir, "FSBL")

- Assegureu-vos que la plataforma de maquinari sigui la que esteu treballant

- Premeu següent (No premeu Finalitza)

- Seleccioneu la plantilla Zynq FSBL

- Feu clic a Finalitza.

- Un cop finalitzat el procés de creació, sabreu si tot ha funcionat si veieu les dues carpetes noves següents a la finestra de l'Explorador de projectes.

-

Crea una imatge d'arrencada Ara hauràs de crear la imatge d'arrencada.

- Feu clic amb el botó dret a la carpeta del vostre projecte (en aquest cas la meva es diu "RTOSDemo")

- Feu clic a "Crea una imatge d'arrencada" al menú desplegable

-

Si tot està enllaçat correctament, el projecte sabrà quins fitxers necessita i es mostrarà la finestra següent com veieu a continuació (la clau és que teniu 3 particions a la secció Imatge d'arrencada, el carregador d'arrencada, el fitxer de bits i el fitxer.elf dels vostres projectes).

Si no és així, és possible que hi hagi algun problema en l'enllaç del vostre projecte. Assegureu-vos que les carpetes del projecte estiguin enllaçades amb els seus respectius BSP

- Feu clic al botó "Crea imatge"

-

L’últim pas que cal dur a terme amb el programari és ara fer flashar la imatge creada anteriorment a la memòria del tauler

- Seleccioneu a la barra d'eines principal de l'SDK seleccioneu Xilinx Tools-> Program Flash Memory

- Assegureu-vos que la plataforma de maquinari correcta estigui seleccionada i que el camí del fitxer d’imatge apunti correctament al fitxer. BIN creat al pas anterior.

- Seleccioneu "qspi single" del tipus Flash

- Marqueu el botó "Verifica després del flaix" per assegurar la integritat, però no és necessari

- Configureu el vostre tauler Finalment, heu d'assegurar-vos que el pont de mode de programació de taules (JP5) està correctament configurat per seleccionar l'arrencada des del qspi (que conté el que acabeu de parpellejar) quan s'executa el BootROM.

- Ara només heu d’encendre el dispositiu i assegureu-vos que el “LED de configuració lògica feta” (LED 10) s’encén de color verd.

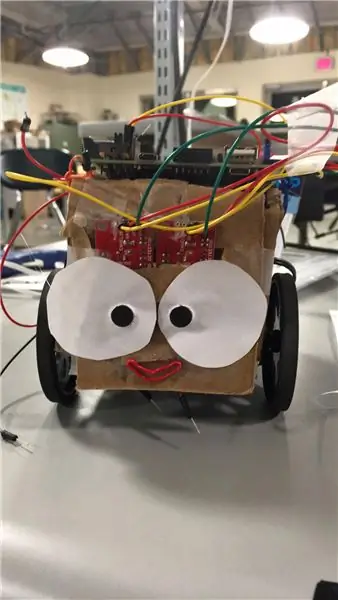

Pas 11: fer que l'Ernie sigui bonic

- Pell

- Molta pell

- Ulls grans!

- … barret de copa

Recomanat:

Bricolatge Com fer un rellotge d’aspecte fresc - StickC - Fàcil de fer: 8 passos

Bricolatge Com fer un rellotge d’aspecte divertit - StickC - Fàcil de fer: en aquest tutorial aprendrem a programar ESP32 M5Stack StickC amb Arduino IDE i Visuino per mostrar una hora a la pantalla LCD i també configurar l’hora mitjançant els botons StickC

Com fer un comptador de passos ?: 3 passos (amb imatges)

Com fer un comptador de passos ?: Jo solia tenir un bon rendiment en molts esports: caminar, córrer, anar en bicicleta, jugar a bàdminton, etc. M’encanta viatjar poc després. Bé, mireu el meu ventre corpulent … Bé, de totes maneres, decideixo tornar a començar a fer exercici. Quin equip he de preparar?

(2) Començar a fer un joc: fer una presentació a Unity3D: 9 passos

(2) Començar a fer un joc: fer una pantalla de presentació a Unity3D: en aquest instructiu aprendreu com fer una pantalla de presentació senzilla a Unity3D. En primer lloc, obrirem Unity

Com fer un robot de seguiment de línia sense fer servir Arduino (microcontrolador): 5 passos

Com fer un robot de seguiment de línia sense utilitzar Arduino (microcontrolador): en aquest instructiu, us ensenyaré a fer un robot de seguiment de línia sense utilitzar Arduino. Faré passos molt senzills per explicar-lo. Aquest robot utilitzarà el sensor de proximitat IR per seguiu la línia. No necessitareu cap tipus d’experiència de programació per

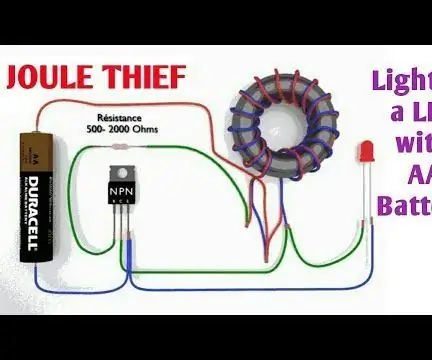

Circuit de lladres Joule Com fer i fer un circuit Explicació: 5 passos

Circuit de Joule Thief Com fer i fer un circuit Explicació: Un "Joule Thief" és un circuit de reforç de tensió simple. Pot augmentar la tensió d’una font d’energia canviant el senyal de baixa tensió constant en una sèrie d’impulsos ràpids a una tensió més alta. El més habitual és que es vegi aquest tipus de circuit que feia servir