Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:14.

- Última modificació 2025-01-23 14:38.

L'objectiu d'aquest projecte és crear la funcionalitat de visualització d'imatges d'un Smart Mirror. El mirall pot mostrar prediccions (assolellat, parcialment assolellat, ennuvolat, ventós, pluja, trons i neu) i valors de temperatura des de -9999 ° fins a 9999 °. Els valors de previsió i temperatura es codifiquen de manera dura, com si volguessin emular-los analitzats des d’una API meteorològica.

El projecte utilitza una placa Zynq-Zybo-7000 que executa FreeRTOS i utilitza Vivado 2018.2 per dissenyar i programar el maquinari.

Parts:

Zynq-Zybo-7000 (amb FreeRTOS)

LCD de 19 (640x480)

Cable VGA

Mirall acrílic de 12 "x 18"

Pas 1: Configuració de Vivado

Descarregueu Vivado 2018.2 de Xilinx i utilitzeu la llicència Webpack. Inicieu Vivado i "Crea un projecte nou" i doneu-li un nom. A continuació, seleccioneu "Projecte RTL" i marqueu "No especifiqueu fonts en aquest moment". En seleccionar una peça, seleccioneu "xc7z010clg400-1" i premeu "Finalitza" a la pàgina següent.

Pas 2: Embalatge de l'IP del controlador VGA

Afegiu el fitxer vga_driver.sv a les fonts de disseny. A continuació, feu clic a "Eines" i seleccioneu "Crea i empaqueta una nova IP". Seleccioneu "Empaqueu el vostre projecte actual". A continuació, trieu una ubicació IP i "Incloeu fitxers.xci". Feu clic a "D'acord" a la finestra emergent i, a continuació, a "Finalitza".

A "Passos per empaquetar", aneu a "Revisa i empaqueta" i seleccioneu "Paquet IP".

Ara el vga_driver hauria d’estar disponible com a bloc IP.

Pas 3: IP de Zynq

A la secció "Integrador d'IP", seleccioneu "Crea disseny de blocs". Afegiu el "Sistema de processament ZYNQ7" i feu doble clic al bloc. Feu clic a "Importa la configuració de XPS" i pengeu el fitxer ZYBO_zynq_def.xml.

A continuació, a "Configuració PS-PL", obriu el menú desplegable per a "AXI Non Secure Enablement" i marqueu "M AXI GP0 interface".

A continuació, a "Configuració MIO", obriu el menú desplegable per a "Unitat de processador d'aplicacions" i marqueu "Temporitzador 0" i "Gos de vigilància".

Finalment, a "Configuració del rellotge", obriu el menú desplegable per a "Rellotges de tela PL" i marqueu "FCLK_CLK0" i a 100 MHz.

Pas 4: IP GPIO

Afegiu dos blocs GPIO al disseny de blocs. Els GPIO s’utilitzaran per controlar l’adreça del píxel i els components RGB dels píxels. Configureu els blocs tal com es mostra a les imatges anteriors. Un cop hàgiu afegit i configurat els dos blocs, feu clic a "Executa l'automatització de la connexió".

GPIO 0: el canal 1 controla l'adreça del píxel i el canal 2 controla el color vermell.

GPIO 1: el canal 1 controla el color verd i el canal 2 controla el color blau.

Pas 5: bloquejar la memòria

Afegiu una IP de generador de memòria de blocs al disseny de blocs i configureu-la tal com es mostra a dalt. Els colors dels píxels s’escriuen a les adreces de memòria que després llegeix el controlador VGA. La línia d’adreça ha de coincidir amb la quantitat de píxels que s’utilitzen, de manera que ha de ser de 16 bits. Les dades incloses també són de 16 bits, ja que hi ha 16 bits de color. No ens importa llegir cap bit de confirmació.

Pas 6: una altra IP

El pdf adjunt mostra el disseny de blocs completat. Afegiu la IP que falta i completeu les connexions. També "Feu externs" per a les sortides de color VGA i les sortides de sincronització vertical i horitzontal.

xlconcat_0: concatena els colors individuals per formar un senyal RGB de 16 bits que s’alimenta a la memòria RAM del bloc.

xlconcat_1: concatena els senyals de columna i fila del controlador VGA i s’introdueix al port B del bloc RAM. Això permet al controlador VGA llegir els valors de color dels píxels.

VDD: Constant HIGH connectat a l’habilitació d’escriptura de la memòria RAM de bloc perquè sempre hi puguem accedir.

xlslice_0, 1, 2 - Les llesques s'utilitzen per trencar el senyal RGB en senyals R, G i B individuals que es poden alimentar al controlador VGA.

Un cop s'hagi completat el disseny del bloc, creeu un embolcall HDL i afegiu el fitxer de restriccions.

* El disseny de blocs es basa en el tutorial escrit per benlin1994 *

Pas 7: SDK

A continuació s’inclou el codi que executa aquest disseny de blocs. Init.c conté les funcions que gestionen el dibuix (previsions, números, símbol de grau, etc.). El bucle principal de main.c és el que s’executa quan es programa la placa. Aquest bucle estableix els valors de predicció i temperatura i, a continuació, crida a les funcions de dibuix a init.c. Actualment repassa les set previsions i es visualitza una darrere l’altra. Es recomana afegir un punt de trencament a la línia 239 per poder veure cada imatge. El codi es comenta i us proporcionarà més informació.

Pas 8: Conclusió

Per millorar el projecte actual, es podrien penjar imatges de previsió de precàrrega en forma de fitxers COE a Block Memory Generators. Per tant, en lloc de dibuixar les previsions manualment, tal com vam fer al codi C, es podrien llegir les imatges. Hem intentat fer-ho però no hem pogut fer funcionar. Vam poder llegir valors de píxels i enviar-los, però va crear imatges desordenades que no s’assemblaven a les que vam penjar a la memòria RAM. El full de dades del Generador de memòria de blocs és útil per llegir.

El projecte és essencialment la meitat d’un Smart Mirror, ja que no té l’aspecte de connectivitat a Internet. Si afegiu això, es proporcionaria un Smart Mirror complet.

Recomanat:

Feu un rellotge de mirall infinit: 15 passos (amb imatges)

Feu un rellotge de mirall infinit: en un projecte anterior vaig construir un mirall infinit, on el meu objectiu final era convertir-lo en un rellotge. (Feu un mirall infinit de colors) No ho vaig perseguir després de construir-lo perquè, tot i que semblava genial, hi havia algunes coses

Feu un cub de mirall EASY Infinity - SENSE impressió 3D ni programació: 15 passos (amb imatges)

Feu un cub de mirall EASY Infinity | SENSE impressió 3D ni programació: a tothom li agrada un bon cub infinit, però sembla que seria difícil de fer. El meu objectiu per a aquest instructiu és mostrar-vos pas a pas com fer-ne un. No només això, sinó que amb les instruccions que us dono, podreu fer-ne un

Mirall d'afirmació electrònica: 8 passos (amb imatges)

Mirall d’afirmació electrònica: quan us mireu al mirall, qui no podria fer servir algunes paraules d’ànim? Construïu una pantalla dins d’un mirall per desplaçar-vos per les afirmacions personalitzades que podeu llegir sobre el vostre propi reflex. Aquest elegant projecte es combina fàcilment amb un shadowbo comprat a la botiga

Mirall de vanitat de bricolatge en passos senzills (amb llums de tira LED): 4 passos

Mirall de vanitat de bricolatge en passos senzills (amb llums de tires LED): en aquest post vaig crear un mirall de vanitat de bricolatge amb l'ajut de les tires LED. És molt genial i també heu de provar-les

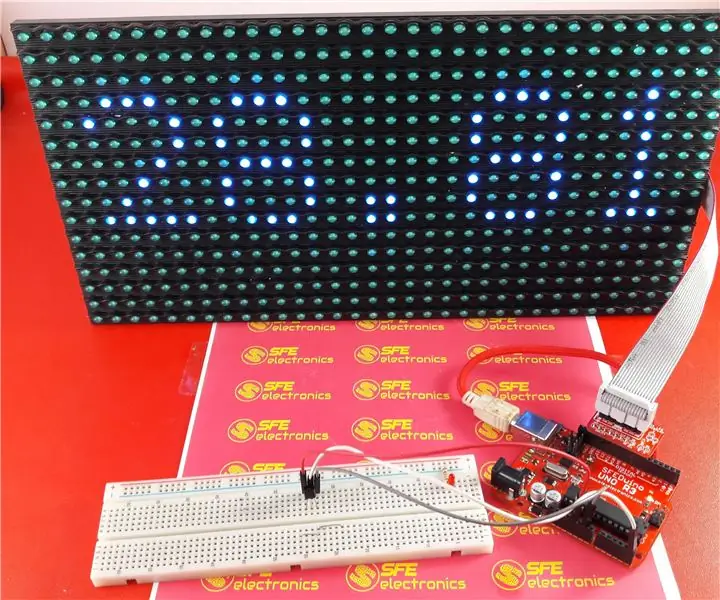

Temperatura de visualització al mòdul de visualització LED P10 mitjançant Arduino: 3 passos (amb imatges)

Temperatura de visualització al mòdul de visualització LED P10 mitjançant Arduino: en el tutorial anterior s’ha explicat com mostrar text al mòdul de visualització LED Dot Matrix P10 mitjançant Arduino i el connector DMD, que podeu consultar aquí. En aquest tutorial oferirem un senzill tutorial de projecte mitjançant el mòdul P10 com a mitjà de visualització