Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:13.

- Última modificació 2025-01-23 14:37.

Mai heu imaginat com el vostre teclat pren entrada i com s’emmagatzemen aquestes dades. Aquest projecte és una versió més petita d’entrada i emmagatzematge de dades. Una explicació elaborada de com el senyal de les tecles i el rellotge afecten els elements de memòria (xancles).

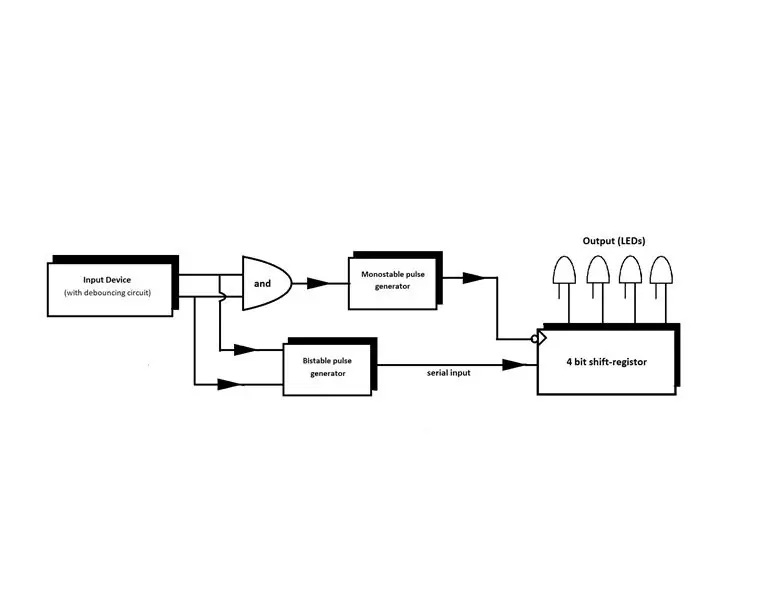

Pas 1: diagrama de blocs

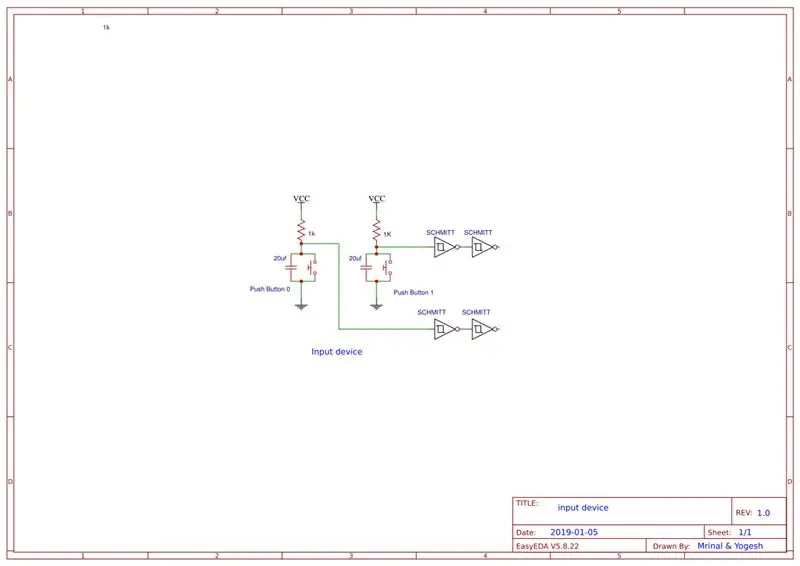

1. Dispositiu d'entrada

Com a dispositiu d’entrada binari de 4 bits, només hi ha 2 botons polsadors (un per registrar 1 (alt) i un altre per 0 (baix) amb un filtre de soroll necessari per generar el senyal d’entrada. El senyal de sortida generat és un pols zero (quan la tecla es prem el senyal sempre alt canvia a baix).

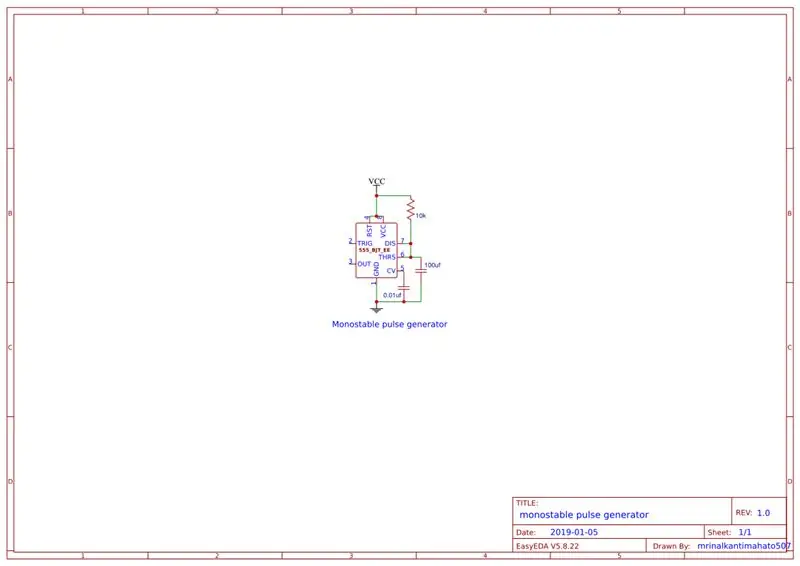

2. Generador de polsos monoestables

Els senyals d’entrada s’introdueixen al generador d’impulsos monoestables per generar un impuls que té una durada fixa de temps elevat, que s’activa pel petit impuls d’entrada. Aquest pols monoestable s’utilitza com a entrada de rellotge al registre de desplaçament.

3. Generador de pols biestable

Aquest pols també és impulsat per les línies de senyal d'entrada, quan es prem la tecla (alta) aquest senyal es configura i es reinicia quan es prem la tecla baixa. El senyal s’alimenta com a entrada serial esquerra al registre de desplaçament.

4. Registre de majúscules

El registre de desplaçament de 4 bits utilitza 4 xancles per emmagatzemar dades. Es necessita una entrada de sèrie amb un rellotge per emmagatzemar les dades d’esquerra a dreta o de dreta a esquerra. En aquest projecte, les dades de sèrie que fem servir provenen del generador de polsos Bi-estable i el senyal de rellotge del generador de polsos monoestables.

5. Sortida

Els LED indiquen la sortida.

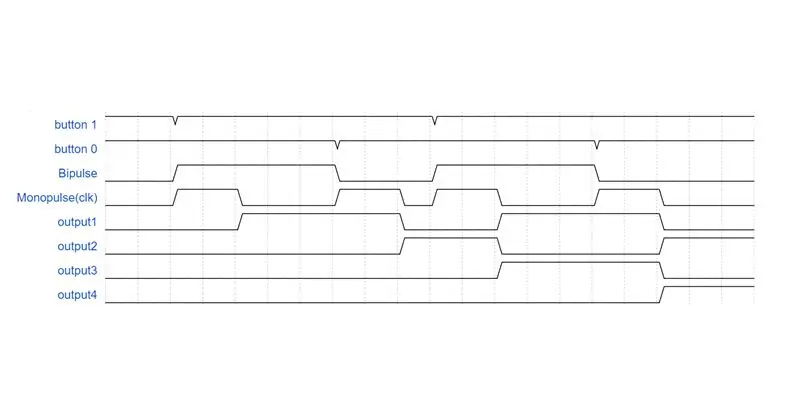

Pas 2: Diagrama de temps

Un diagrama de temporització de mostra que pren una entrada 0101. El pols d'entrada del botó 1 i el botó 2 tenen un "temps baix" molt petit, per això es mostra com un pic al diagrama de temps.

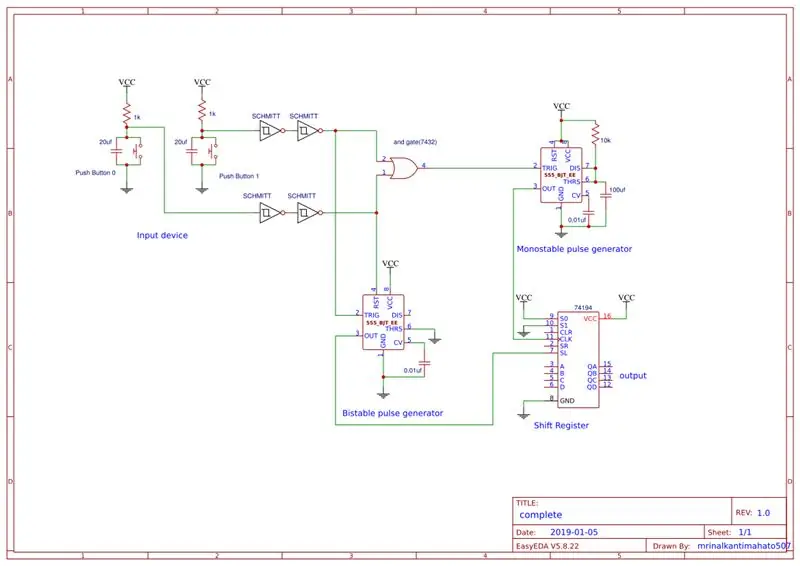

Pas 3: diagrama del circuit

El temps alt per al pols monoestable es pot canviar canviant el valor de RC (valor de resistència i capacitat). El temps alt és donat per t = 1,1 * RC. El temps alt té un límit inferior que depèn de l’interruptor denunciant utilitzat, el límit és generalment 10-20 ms. El temps més alt en aquest disseny de circuits és d’1 s (10 k omh * 100uf).

Això, reduint aquest temps, augmenta la velocitat del dispositiu.

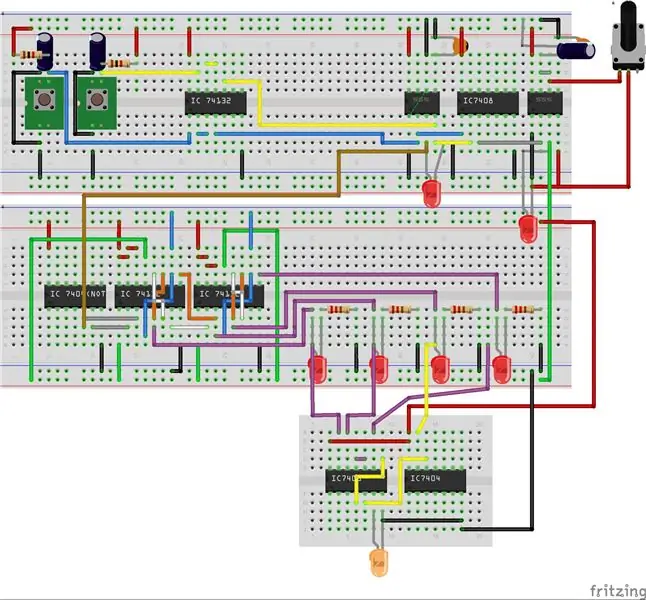

Pas 4: Disseny Fritzing amb fitxers BOM

Descarregueu el fitxer fritzing per personalitzar el disseny i crear el vostre propi disseny.

La llista de components necessaris es troba al fitxer BOM.

Recomanat:

Dispositiu ASS (dispositiu social antisocial): 7 passos

Dispositiu ASS (dispositiu social antisocial): digueu que sou la persona que li agrada estar a prop de la gent però que no li agrada que s’acosti massa. També ets agradable a la gent i et costa dir no a la gent. Per tant, no sabeu com dir-los que es retirin. Bé, entreu: el dispositiu ASS. S

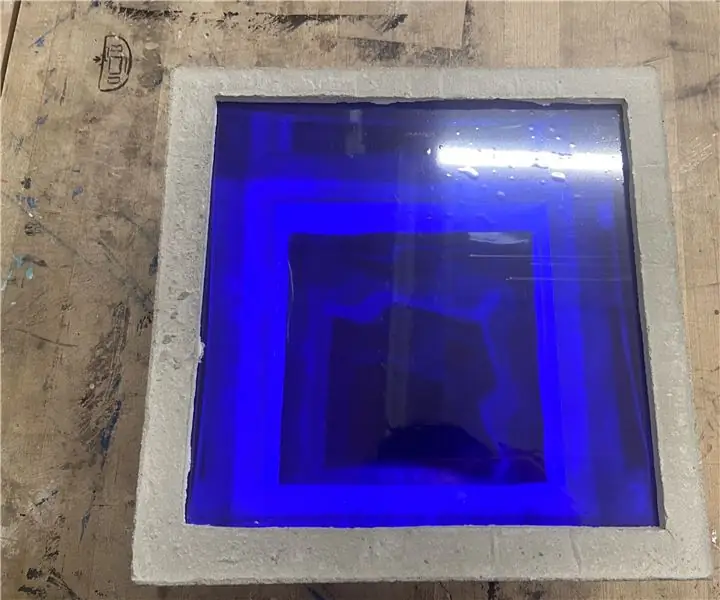

Dispositiu LED amb Bluetooth: entrada per a una altra dimensió: 6 passos

Dispositiu LED amb Bluetooth: entrada per a un altre espai de dimensió: es tracta d’un dispositiu de llum LED per al meu projecte d’escultura anomenat Sacred Object. Estic fent servir aquest dispositiu per presentar una entrada per a un món nou. Quan encenc el llum LED, podem veure un túnel infinit dins de la caixa de formigó. La tira LED és de control

OrangeBOX: Dispositiu d'emmagatzematge de còpia de seguretat segur basat en OrangePI: 5 passos

OrangeBOX: Dispositiu d'emmagatzematge de còpia de seguretat segur basat en OrangePI: OrangeBOX és una caixa de seguretat d'emmagatzematge remot tot en un per a qualsevol servidor. El vostre servidor es pot infectar, corrompre, esborrar i totes les vostres dades encara estan segures a OrangeBOX i a qui no els agradaria una missió impossible, com ara un dispositiu de còpia de seguretat, del que acabeu de pl

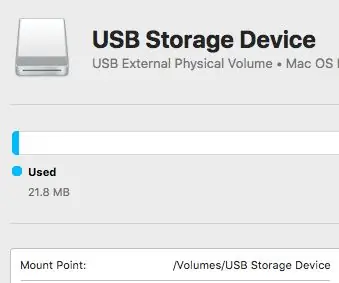

Com tornar a formatar un dispositiu d'emmagatzematge extern mitjançant Mac OS X: 10 passos

Com tornar a formatar un dispositiu d'emmagatzematge extern amb Mac OS X: vendre un USB antic? O ordinador? Utilitzeu aquesta senzilla guia pas a pas per tornar a formatar el dispositiu d’emmagatzematge extern al Mac. Els avantatges d’aquest formatatge del disc dur són la seguretat, la comoditat i la reutilització. Això ajudarà a m

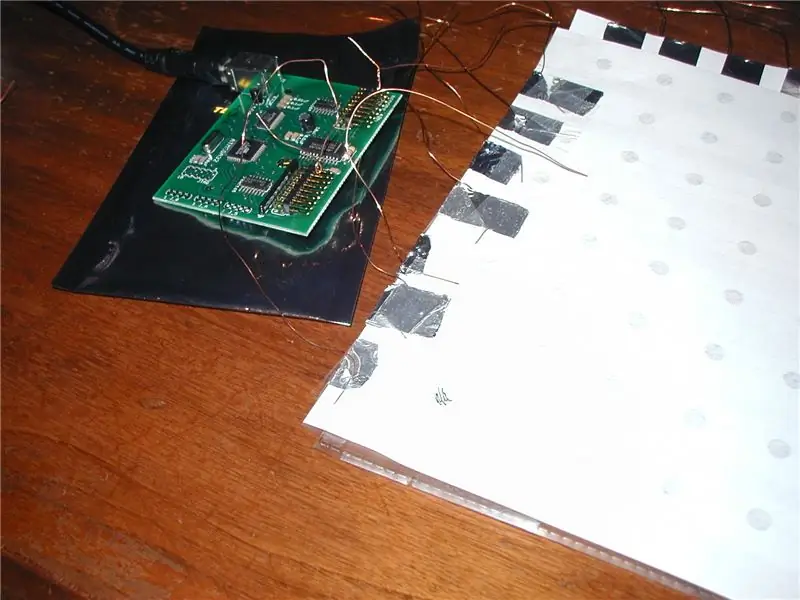

Dispositiu d’entrada de paper i llauna: 5 passos

Dispositiu d’entrada de paper i llauna: aquesta guia us mostrarà com fer un dispositiu d’entrada barat i lleig per al vostre ordinador. En això utilitzo una placa lògica monome de 40 hores per enviar els senyals a l’ordinador des d’una xarxa de botons de vuit per vuit, però aquests plans es podrien modificar fàcilment per