Taula de continguts:

- Pas 1: Funcionament de l'usuari del seqüenciador digital

- Pas 2: detalls tècnics

- Pas 3: detalls tècnics

- Pas 4: divisor de rellotge de 7 segments

- Pas 5: divisor de rellotge per pulsacions per minut

- Pas 6: Divisió de rellotge de parcel·les

- Pas 7: Reprodueix / Pausa / Selecciona la màquina d'estat

- Pas 8: Reprodueix / Pausa / Selecciona la màquina d'estat

- Pas 9: sortida FSM

- Pas 10: sortida FSM

- Pas 11: Assignació de notes

- Pas 12: selecció de sortida

- Pas 13: Square Wave Gen

- Pas 14: pantalla de 7 segments

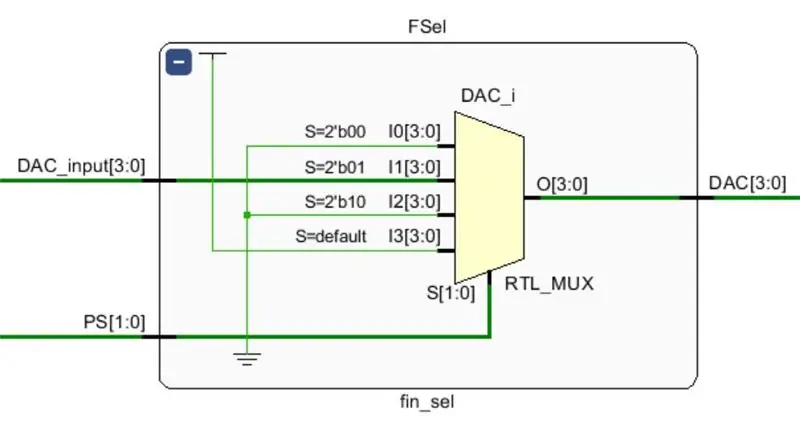

- Pas 15: selecció final

- Pas 16: Dispositius externs: DAC

- Pas 17: Dispositius externs: altaveu

- Pas 18: demostració de vídeo

- Pas 19: codi VHDL

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:16.

- Última modificació 2025-01-23 14:38.

CPE 133, Cal Poly San Luis Obispo

Creadors de projectes: Jayson Johnston i Bjorn Nelson

A la indústria musical actual, un dels "instruments" més utilitzats és el sintetitzador digital. Tots els gèneres musicals, des del hip-hop fins al pop i fins i tot el country, utilitzen un sintetitzador digital a l’estudi per crear els ritmes i els sons que necessiten per donar vida a la seva música. En aquest tutorial, crearem un sintetitzador molt senzill amb la placa FPGA Basys 3.

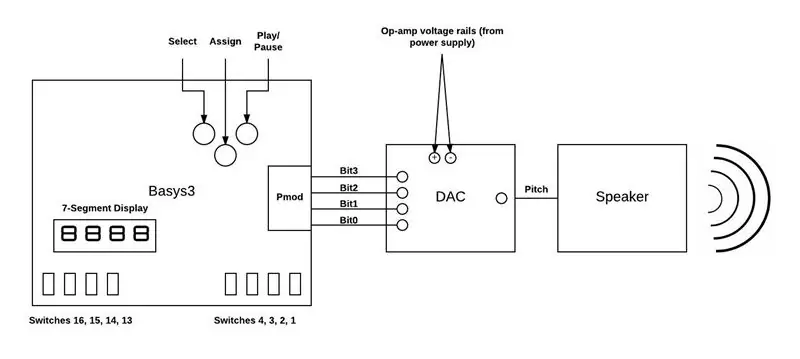

El sintetitzador podrà reproduir quatre notes de quart seleccionades a un nombre constant de pulsacions per minut. Els usuaris utilitzaran els commutadors per assignar cada nota de quart a un to musical. Per a aquest projecte estem utilitzant un convertidor digital a analògic de 4 bits (DAC) per prendre la sortida de la placa i convertir-la en un senyal analògic. La sortida del DAC s’alimentarà a un altaveu estàndard de l’ordinador, creant la nostra música. Són setze tocs discrets possibles. Limitarem el nostre sintetitzador a una sola octava de 12 notes, que es situen entre C mig (261,6 Hz) i B4 (493,9 Hz). L'usuari també tindrà l'opció d'assignar diverses notes al mateix temps, així com assignar un descans fent clic a assignar sense tenir cap dels commutadors de tonalitat desplaçats cap amunt. A mesura que cada nota es selecciona i es reprodueix, la nota de lletra es mostra a la pantalla de 7 segments. També farem servir tres dels botons del tauler, un per reproduir i posar en pausa la música, un per restablir el sintetitzador i posar-lo en mode de “selecció” i el tercer per assignar a cada nota un to mentre estigui en mode de selecció.

Un cop l'usuari estigui satisfet amb la seva elecció de notes i després de prémer el botó de reproducció, el sintetitzador reproduirà cada nota de forma successiva repetidament fins que l'usuari prem la pausa o la selecció.

Aquí teniu una llista de l’equip necessari:

- Vivado (o qualsevol espai de treball VHDL)

- Basys 3 o placa FPGA similar

- Convertidor digital a analògic (mínim de 4 bits)

- Altaveu amb presa per a auriculars

- Conductors de filferro

Pas 1: Funcionament de l'usuari del seqüenciador digital

Els passos següents són fer servir el seqüenciador digital. El seqüenciador digital admet la reproducció de 12 tons diferents (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), que oscil·len entre 261,6 Hz i 493,9 Hz.

1. Premeu el botó esquerre per posar el tauler en mode de selecció. Quan es troba en aquest mode, els 4 commutadors situats a l’esquerra (commutadors 13 a 16) s’utilitzaran cadascun per emmagatzemar un valor de to diferent.

2. Per fer una selecció, gireu un dels interruptors de l'esquerra i, a continuació, utilitzeu els 4 interruptors de la dreta (commutadors de l'1 al 4) per triar el to desitjat. El to associat a una combinació específica d’interruptors de la dreta es mostrarà a la pantalla de set segments i la pantalla s’actualitzarà al nou to associat sempre que els commutadors de la dreta es canvien a una nova combinació. Es pot assignar un descans sense assignar mai un to a un dels commutadors esquerres, o assignant un to mostrat com 0 a la pantalla a la nota. Quan s'hagi trobat el to desitjat i es mostri a la pantalla, premeu el botó d'assignació inferior per assignar aquest to específic a la nota.

3. Repetiu el pas 2 per a les tres notes restants, donant la volta a cada interruptor esquerre restant activat individualment, triant el to corresponent amb els interruptors de la dreta i prement el botó inferior per assignar el to a la nota. Es poden assignar diverses notes a la mateixa afinació canviant més d'un commutador esquerre cap amunt alhora.

4. Ara que s'han assignat tots els tons de notes, el seqüenciador digital està a punt per reproduir-se. Per reproduir les notes a l’altaveu, només cal que premeu el botó dret de reproducció / pausa per començar a reproduir la música. L'ordre de la seqüència de reproducció reflecteix els tons associats als commutadors esquerra, d'esquerra a dreta. Les notes es reproduiran a un nombre fix de pulsacions per minut, en l’ordre 1, 2, 3, 4, 1, 2 …. La pantalla mostrarà la nota que s'està reproduint actualment mentre els altaveus toquen la música. Per posar en pausa la reproducció de la música, només cal que premeu el botó dret i la música deixarà de reproduir-se i es mostrarà un símbol de pausa a la pantalla. Si torneu a prémer el botó dret, es reprendrà la reproducció.

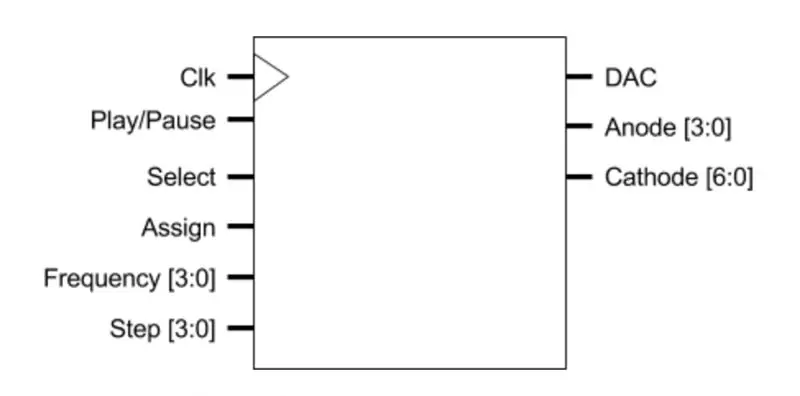

Pas 2: detalls tècnics

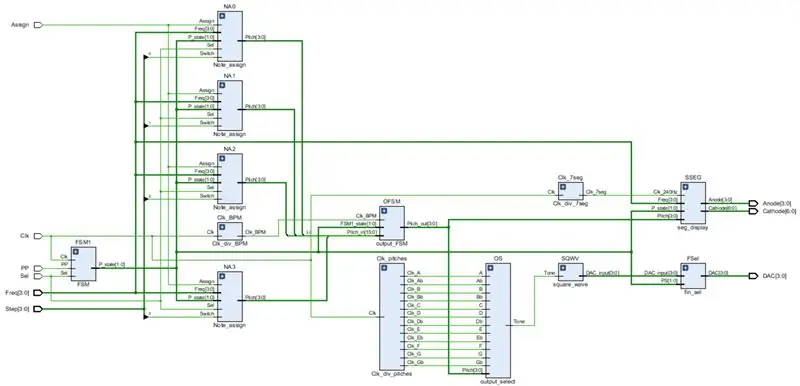

El nostre sintetitzador utilitza molts components digitals diferents. S'inclouen màquines d'estat finit, registres, multiplexors, divisors de rellotge i molt més. Per construir el nostre sintetitzador, hem utilitzat 10 fitxers modulars únics. En lloc de convertir cada mòdul en un component, hem desglossat els fitxers modulars per funció. Com a resultat, la majoria de mòduls són més d’un component. Tingueu en compte que la imatge superior mostra tots els blocs units entre si en el nostre disseny superior.

Discutirem cada mòdul descrivint les entrades i sortides, desglossant-ne els components i explicant el seu propòsit en el disseny general. S'inclou un fitxer ZIP a la part inferior de l'informable, que conté tots els fitxers de codi VHDL utilitzats al projecte.

Entrades

- Clk (senyal de rellotge natiu)

- PP (reproducció / pausa)

- Sel (posa el sintetitzador en mode de selecció)

- Assigna (assigna un pas a un to)

- Pas (les notes posicionals)

- Freq (els commutadors que creen el to desitjat)

Sortides

- Ànode (ànodes de 7 segments)

- Càtode (càtodes de 7 segments)

- DAC (4 bits que condueix el DAC)

Pas 3: detalls tècnics

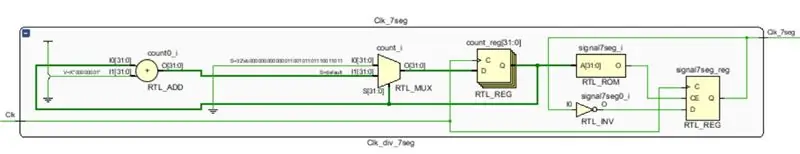

Pas 4: divisor de rellotge de 7 segments

El nostre sintetitzador fa servir tres divisors de rellotge, tots ells produeixen senyals que tenen un propòsit diferent en el nostre projecte. Un divisor de rellotge pren un senyal de rellotge natiu i produeix un senyal alterat que té una freqüència inferior a la del senyal de rellotge original. El rellotge natiu del Basys 3 és de 100 MHz. Aquesta és la freqüència que utilitzen els nostres separadors de rellotge. Si feu servir una placa FPGA diferent amb una freqüència de rellotge nativa diferent, és possible que hagueu d’alterar el codi.

El divisor de rellotge de 7 segments produeix un senyal que condueix el fitxer seg_display. Explicarem com funciona aquest fitxer amb més detall quan arribem a la seva secció. Bàsicament, aquest divisor de rellotge produeix un senyal de 240 Hz que s’utilitzarà per canviar entre ànodes i càtodes de la pantalla. El senyal és de 240 Hz perquè la freqüència amb què l’ull humà no pot reconèixer l’absència de llum és de 60 Hz. Estem fent servir dos dígits, de manera que en doblar aquesta freqüència, cada dígit oscil·larà a 60 Hz. Aleshores el duplicem per aconseguir 240 Hz perquè el sistema només canvia quan el senyal augmenta, no quan baixa.

Per aconseguir-ho, el divisor pren el senyal natiu de 100 MHz i compta a cada vora ascendent. Quan el comptador arriba a 416667, la sortida passarà de menor a major, o viceversa.

Entrades

Clk (senyal de rellotge natiu)

Sortides

Clk_7seg (a seg_display)

Components

- D registre

- MUX

- Inversor

- Sumador

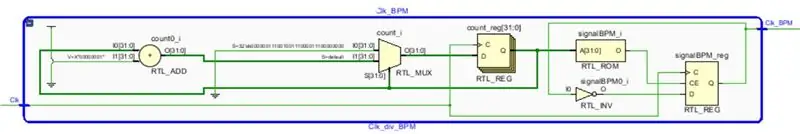

Pas 5: divisor de rellotge per pulsacions per minut

El divisor de rellotge BPM funciona de manera similar. Aquest divisor produeix la freqüència de rellotge que impulsa el canvi entre els quatre passos quan es produeixen tons en estat de reproducció. Vam decidir canviar entre notes a 100 BPM. A 100 BPM, cada nota es reproduirà durant 3/5 segons. El senyal resultant tindria una freqüència d’1,67 Hz.

Per produir un senyal d'aquesta freqüència, vam tornar a utilitzar un sistema de comptatge, però aquesta vegada el recompte va ser de 60 milions. Cada vegada que el comptador arribava als 60 milions, el senyal de sortida canviava per alt o per baix.

Entrades

Clk (freqüència de rellotge nativa)

Sortides

Clk_BPM (a sortida_FSM)

Components

- D registre

- MUX

- Inversor

- Sumador

Pas 6: Divisió de rellotge de parcel·les

El divisor de rellotge Pitches és el més gran dels nostres separadors de rellotge. Aquest divisor emet 12 senyals diferents corresponents a les 12 notes diferents que pot reproduir el nostre sintetitzador. Utilitzant coneixements bàsics de teoria musical, vam deduir que un bit o un bus podria oscil·lar a un ritme que correspon a la freqüència de les notes musicals. Per veure les freqüències que hem utilitzat, mireu aquí. Hem utilitzat la quarta octava de llançaments.

Aquí s’utilitza el mateix sistema de recompte. Per obtenir els valors específics que hem comptabilitzat, consulteu el fitxer anomenat Clk_div_pitches.

Entrades

Clk (freqüència de rellotge nativa)

Sortides

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (per seleccionar_de sortida)

Components

- D registre

- MUX

- Inversor

- Sumador

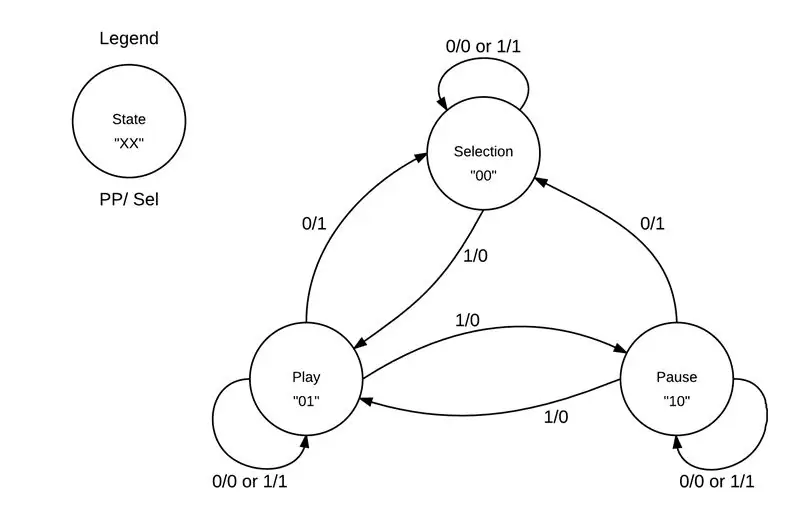

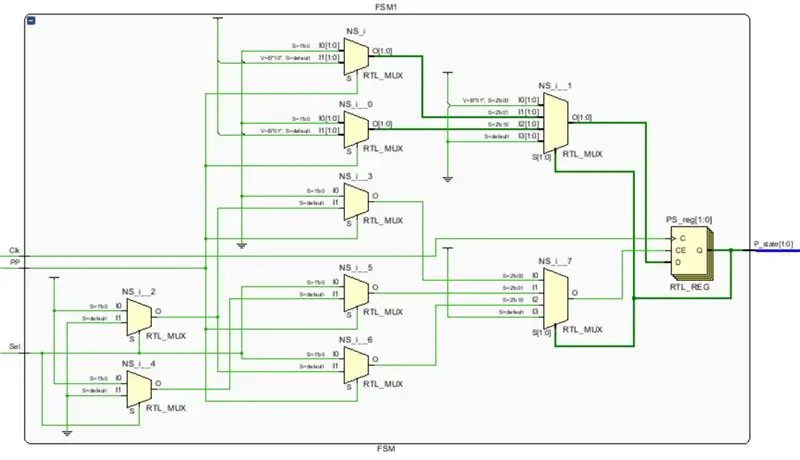

Pas 7: Reprodueix / Pausa / Selecciona la màquina d'estat

Al nostre projecte hi ha dues màquines d’estats finits (FSM). Un FSM és un dispositiu lògic que només pot existir en un estat d'una quantitat d'estats finits. Mitjançant un FSM, un circuit digital pot passar a un nou estat basat en una combinació d’entrades. Utilitzant la lògica d’entrada, l’estat d’un FSM canviarà quan hi hagi una vora ascendent del rellotge. A partir de l'estat i les entrades del circuit, podeu crear una lògica de sortida que doni sortides que només existeixen si el FSM es troba en un estat determinat.

La màquina d’estats PPS és el primer FSM del nostre circuit. Hi ha tres estats en aquest FSM; Mode de reproducció, pausa i selecció. Per desplaçar-nos pels diferents estats, hem utilitzat els botons PP i Selecció. Vegeu el diagrama d'estats anterior per veure com es produeixen les transicions entre estats. Vam fer aquesta transició FSM a la vora ascendent del rellotge natiu de 100 MHz, de manera que seria impossible que la màquina no transís quan es premia un dels botons, fins i tot durant un temps molt curt. L'estat actual (P_state) és l'única sortida d'aquest mòdul.

Entrades

- Clk (freqüència de rellotge nativa)

- Sel (botó esquerre)

- PP (botó dret)

Sortides

P_state (estat actual, a output_FSM, note_assign, seg_dsiplay, final_select)

Components

- MUX

- D registre

Pas 8: Reprodueix / Pausa / Selecciona la màquina d'estat

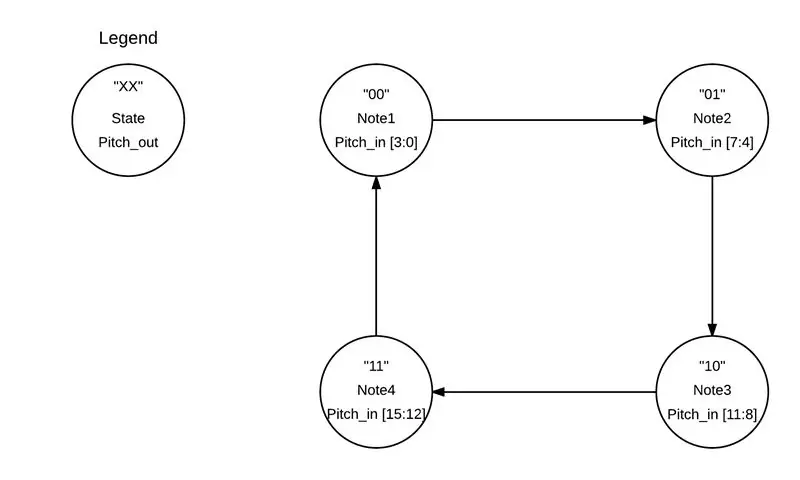

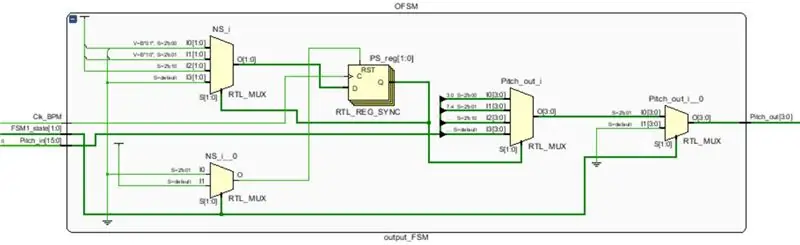

Pas 9: sortida FSM

Aquest és el segon FSM a què fa referència l’apartat anterior. Aquest FSM té una funció diferent de l’altra, però la base d’aquest és bàsicament la mateixa.

El FSM de sortida només funciona si l'estat actual del primer FSM és "01" (l'estat de reproducció). Bàsicament, aquesta és l’habilitació del mòdul. Si l'estat és "01", l'FSM canviarà entre estats a la vora ascendent del senyal de rellotge BPM. Ho fem perquè output_FSM controla quin número binari per al to seleccionat s'envia als mòduls output_select i seg_display. El FSM té una entrada de 16 bits provinent del mòdul d'assignació de notes, que es tractarà a continuació. A l'estat "00" per a output_FSM, el mòdul emetrà "xxxx" per a la primera nota assignada. A continuació, a "01", sortirà "aaaa" per a la segona nota i així successivament per a cada nota abans de tornar a la primera nota. Vegeu el diagrama d’estats anterior.

Aquest FSM difereix del primer perquè no hi ha cap lògica d’entrada per controlar el canvi entre estats. En canvi, el FSM només funcionarà quan l'estat del primer FSM sigui "01", i després aquest FSM transitarà entre estats només a la vora ascendent del senyal del rellotge. Una altra diferència és que aquest mòdul té una lògica de sortida, és a dir, que no genera l'estat actual, sinó que genera el número binari del to en aquest estat.

Entrades

- Clk_BPM (senyal de rellotge BPM del divisor de rellotge)

- FSM1_state (PS de PPS FSM)

- Pitch_in (llançaments de note_assign)

Sortides

Pitch_out (un to a la vegada, per a output_select i seg_display)

Components

- MUX

- D registre

Pas 10: sortida FSM

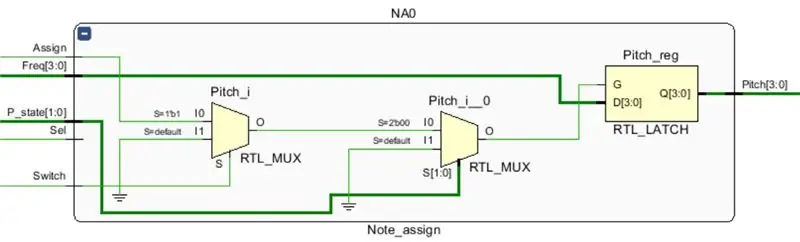

Pas 11: Assignació de notes

El mòdul d'assignació de notes és responsable d'assignar realment un to a la nota de posició, o pas. Aquest mòdul és realment molt senzill. Primer comprova si el circuit es troba en l’estat de "selecció" i si hi ha un commutador de pas (extrem esquerre) alt. Si això és cert i es prem el botó d'assignació, la sortida del mòdul serà igual al nombre binari representat pels commutadors de freqüència (extrem dret).

Originalment, havíem intentat crear un mòdul que realment estalvies un dels senyals de rellotge de pas a la sortida, però vam experimentar problemes amb el canvi de sortida per seguir els senyals de rellotge d’entrada. Aquest és l’únic mòdul utilitzat més d’una vegada en el disseny final. Cada pas té associat un mòdul note_assign i, per això, cada instància del mòdul obté un bit del bus Step.

Entrades

- P_state (estat actual de PPS FSM)

- Sel (botó esquerre)

- Interruptor (interruptor d'un pas)

- Freq (commutadors d'extrema dreta per al to)

- Assigna (botó inferior, assigna una nota)

Sortides

Pitch (número binari, a output_FSM)

Components

- MUX

- D inscripció

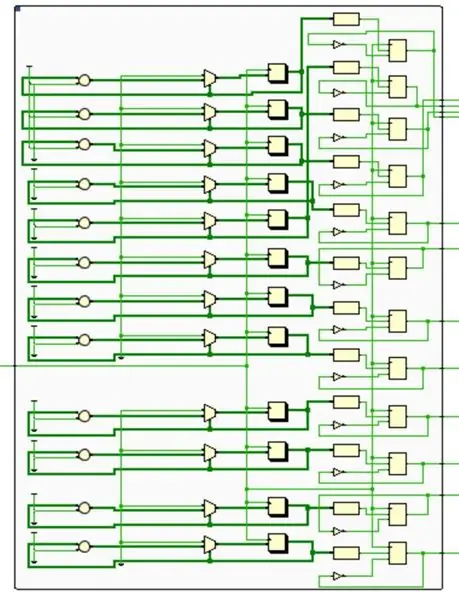

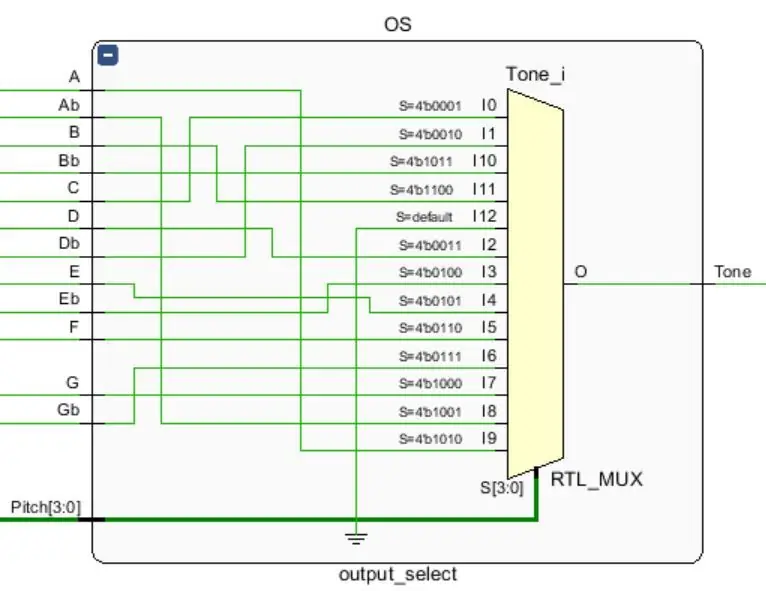

Pas 12: selecció de sortida

La selecció de sortida és responsable d’agafar el número binari d’un to i connectar-lo al seu respectiu senyal de rellotge. Tot i la seva mida, aquest també és un mòdul relativament senzill. Output_select és essencialment un descodificador binari, que descodifica el número binari d'un to a un senyal de rellotge específic. En realitat, assignar la sortida a una freqüència de rellotge va funcionar millor en comparació amb el mòdul note_assign, perquè tot el que havia de fer aquest MUX era el senyal de rellotge amb el número binari que representava l’entrada de control.

Ens disculpem per l’estrany encaminament, Vivado va organitzar els senyals de to alfabèticament per al fitxer clk_div_pitches, però per a aquest fitxer els va organitzar mitjançant un número binari ascendent, cosa que va fer que els tons fossin en un ordre diferent. Tingueu en compte també que si el número binari de output_FSM era "0000" o qualsevol cosa superior a "1100", el MUX va enviar a través d'un senyal pla "0".

Entrada

- Parcel·la (de sortida_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (senyals de rellotge de pas)

Sortida

To (un bit únic que coincideix amb el senyal de rellotge seleccionat, a square_wave)

Components

MUX

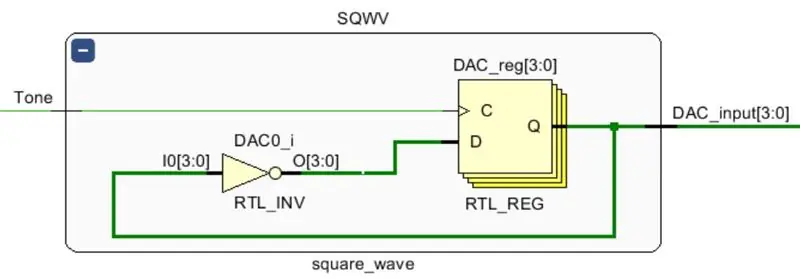

Pas 13: Square Wave Gen

El mòdul square_wave és el generador de l'ona quadrada que es transmet des del tauler al DAC. Mitjançant el senyal de to del fitxer anterior, aquesta ona quadrada inverteix el número de 4 bits entre "0000" i "1111" a la vora ascendent de Tone. El to és una freqüència de to específica, de manera que square_wave produeix una ona amb una freqüència diferent quan output_FSM passa a un altre estat. La sortida de 4 bits d’aquest mòdul es dirigeix al mòdul fin_sel, on la lògica dicta si aquest bus s’expedirà en funció de l’estat de PPS FSM.

Una alternativa a aquest generador d’ones quadrades és produir una ona sinusoïdal. Tot i que és probable que això produeixi un millor to final, és molt més difícil d’implementar, de manera que hem optat per generar una ona quadrada.

Entrades

To (bit oscil·lant de output_select)

Sortides

DAC_input (bus oscil·lant de 4 bits que canvia a la mateixa freqüència de to)

Components

- Inversor

- D registre

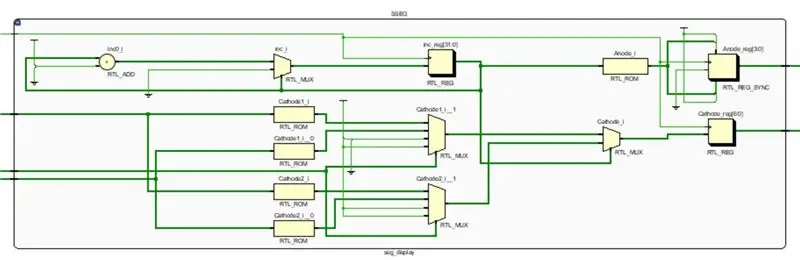

Pas 14: pantalla de 7 segments

El mòdul seg_display controla la pantalla de 7 segments del nostre tauler base. Dins del mòdul, es produeixen dos processos. El primer procés descodifica Freq quan es troba a l'estat de "selecció" o Pitch quan es troba en mode "play". En mode "pausa", el mòdul es descodifica per mostrar el símbol de pausa. Observant el codi VHDL, podeu veure que el descodificador binari realment descodifica l'entrada en dos senyals diferents, càtode1 i càtode2. El càtode1 representa la lletra corresponent al to que es mostrarà i el càtode2 representa el símbol pla (b) si n’hi ha. La raó d'això es relaciona amb el segon procés realitzat pel mòdul seg_display.

En un tauler basys3, la pantalla del segment té càtodes comuns. Mentre els ànodes controlen quin dígit està activat, els càtodes controlen quins segments estan activats. Com que la pantalla té càtodes comuns, això significa que només podeu mostrar un conjunt de segments alhora. Això suposa un problema per a aquest projecte perquè volem mostrar una lletra al primer dígit i el símbol pla, si cal, alhora. Ara recordeu el senyal de rellotge de 7seg? Per solucionar aquest problema, canviem els ànodes i els càtodes d’anada i tornada en el senyal de rellotge de 7seg. Com que el senyal del rellotge és de 240 Hz i fem servir dos dígits, cada dígit oscil·larà a 60 Hz. A l’ull humà, semblarà que els dígits no oscil·len en absolut.

Tingueu en compte també que la pantalla de la placa basys3 utilitza una lògica negativa. Això significa que si un ànode o càtode està definit a '0', aquest dígit o segment estarà activat i viceversa.

Entrades

- Tonalitat (número binari d'una nota, que s'utilitza en estat de reproducció)

- Freq (commutadors de freqüència, que s’utilitzen quan es troba en estat de selecció)

- P_state (estat actual de PPS FSM)

- Clk_240Hz (senyal de rellotge de Clk_div_7seg, doble 120 perquè només estem fent servir la vora ascendent)

Sortides

- Càtode (bus que controla els segments de la pantalla, sortida final)

- Ànode (bus que controla els dígits de la pantalla, sortida final)

Components

- Pestell

- MUX

- D registre

Pas 15: selecció final

La selecció final és l'últim mòdul utilitzat en aquest projecte. Un altre mòdul senzill, aquest mòdul, controla la sortida final que anirà al DAC. Quan es troba a l'estat de "selecció" o "pausa", el mòdul emetrà un "0000" estàtic perquè no es reprodueixi música des dels altaveus. En l'estat "reproduir", el mòdul produirà els 4 bits oscil·lants segons es determini per square_wave.

Entrades

- P_state (estat actual de PPS FSM)

- DAC_input (els 4 bits oscil·lants de square_wave)

Sortides

DAC (és igual a DAC_input en estat de joc, sortida final)

Components

MUX

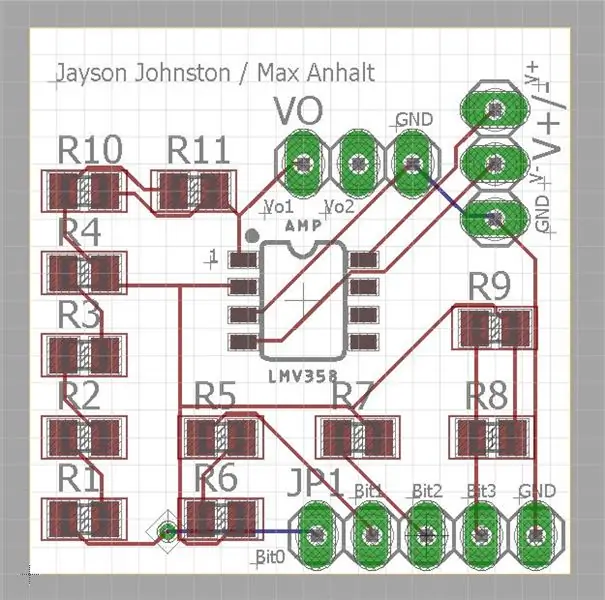

Pas 16: Dispositius externs: DAC

Un convertidor digital a analògic (DAC) pren un senyal discret i el converteix en un senyal continu. El nostre DAC té quatre bits i està fabricat a partir d’un amplificador sumatori. En utilitzar una proporció de resistències en el bucle de subministrament i retroalimentació, vam ser capaços de crear un sistema que produeix sortides a 16 nivells diferents creant mitjançant el "sumat" de cada branca. Bit0, la branca superior, té el menor pes i aporta el potencial més petit quan és elevat a causa de la resistència de les branques. El pes augmenta a mesura que baixes per les branques. Si comptés en binari cap amunt i després retrocediu mitjançant les entrades de bits, les tensions de sortida semblarien una ona sinusoïdal. L'entrada al DAC es va connectar a la dels PMOD de la placa per transferir el senyal de 4 bits.

El DAC es va muntar originalment per a una classe d’Enginyeria Elèctrica i el vam dissenyar i soldar, no comprar-lo en cap botiga. A la part superior es mostra una imatge del fitxer de disseny per crear la placa de circuit imprès.

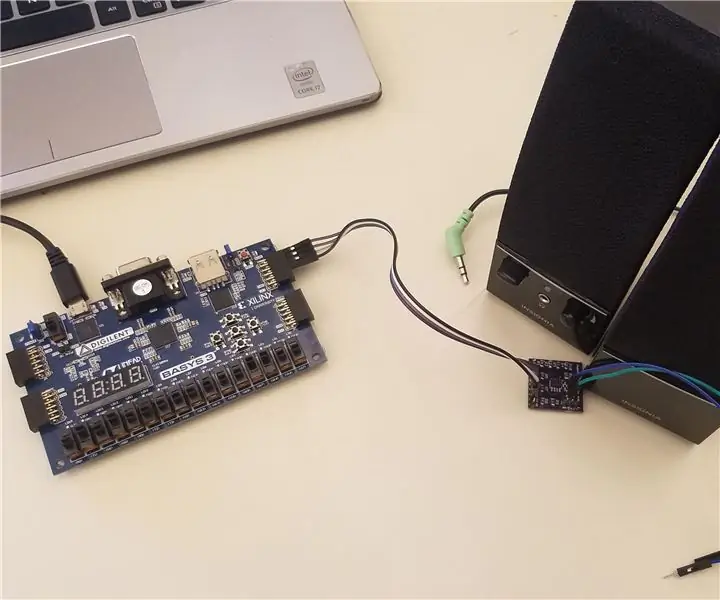

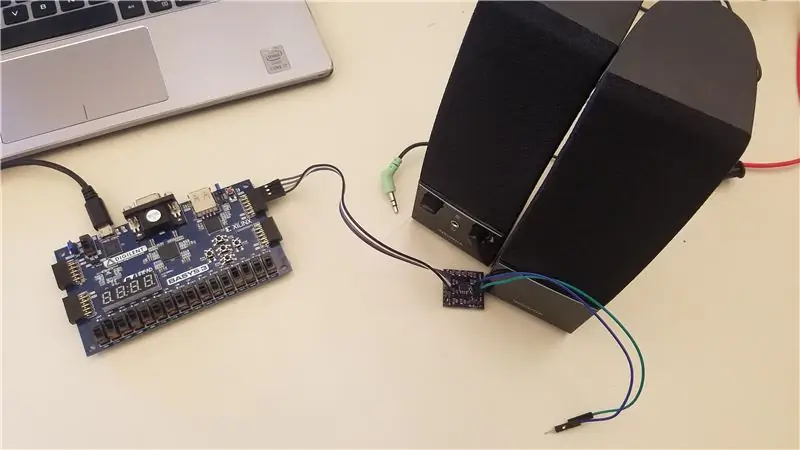

Pas 17: Dispositius externs: altaveu

Per a aquest projecte, no voldreu comprar un parell d’altaveus molt bonics. Com es pot dir, el so és bastant bàsic. Vam anar a comprar un conjunt d’altaveus d’ordinador de 8 dòlars a Best Buy. Tot el que tingui un connector per a auriculars funciona bé. Monotone també funciona bé. Fins i tot podeu utilitzar auriculars, però és possible que els exploteu.

Per connectar la sortida del DAC als altaveus, hem utilitzat cables jumper i, a continuació, hem mantingut el cable de sortida a la punta del connector per a auriculars i el cable per connectar-lo a terra fins a la base. Vam intentar utilitzar cinta elèctrica per mantenir els cables al seu lloc, però va provocar moltes interferències. Provar un estil de cinta diferent podria resoldre aquest problema.

Per als nostres altaveus, els vam girar a la configuració més alta i vam obtenir un soroll decent.

I aquest és l’últim pas per crear un seqüenciador digital a partir d’una placa FPGA. Aneu a les dues seccions següents per descarregar tot el nostre codi VHDL i veure el seqüenciador en acció.

Pas 18: demostració de vídeo

Aquest vídeo mostra la versió final del projecte de treball, inclòs el procés d'assignació dels commutadors a 4 tocs diferents, i els altaveus que toquen les notes respectives.

Pas 19: codi VHDL

Aquí teniu el codi per a tot el projecte, inclosos els fitxers de restricció i sim utilitzats durant la construcció del seqüenciador. Tingueu en compte que els fitxers de disseny que no s’utilitzen ho diuen a l’arquitectura.

Recomanat:

Seqüenciador de seccions de ritme MIDI Arduino: 8 passos (amb imatges)

Seqüenciador de seccions de ritme MIDI Arduino: tenir una bona bateria de programari és fàcil i econòmic avui en dia, però utilitzar un ratolí em mola la diversió. És per això que em vaig adonar del que inicialment es pretenia com un seqüenciador MIDI de bateria de 64 passos de maquinari pur, capaç de provocar fins a 12 diferents elem de bateria

Seqüenciador paral·lel: 17 passos (amb imatges)

Parallel Sequencer Synth: Aquesta és una guia per crear un seqüenciador senzill. Un seqüenciador és un dispositiu que produeix cíclicament una sèrie de passos que després condueixen un oscil·lador. Cada pas es pot assignar a un to diferent i crear així seqüències o efectes d'àudio interessants

Seqüenciador simple: 16 passos (amb imatges)

Seqüenciador simple: una de les claus per fer bona música és la repetició sense sentit. En això és fantàstic el simple seqüenciador. Fa el mateix una i altra vegada en una seqüència de vuit notes. Podeu ajustar la freqüència de la nota, la durada de la nota i

(gairebé) programador universal MIDI SysEx CC (i seqüenciador ): 7 passos (amb imatges)

(gairebé) programador universal MIDI SysEx CC (i seqüenciador …): a mitjan anys vuitanta, els fabricants de sintetitzadors van iniciar un "menys és millor" procés que va conduir a sintetitzadors de barebones. Això va permetre la reducció de costos per part del fabricant, però va fer que el procés de pegat fos tediuos, si no impossible, per a l'ús final

Seqüenciador LED RGB programable (amb Arduino i Adafruit Trellis): 7 passos (amb imatges)

Seqüenciador LED RGB programable (amb Arduino i Adafruit Trellis): els meus fills volien que les tires LED de color il·luminessin els seus escriptoris i no volia fer servir un controlador de tires RGB enllaçat, perquè sabia que s’avorrien amb els patrons fixos tenen aquests controladors. També vaig pensar que seria una gran oportunitat per crear