Taula de continguts:

- Autora John Day day@howwhatproduce.com.

- Public 2024-01-30 08:13.

- Última modificació 2025-01-23 14:37.

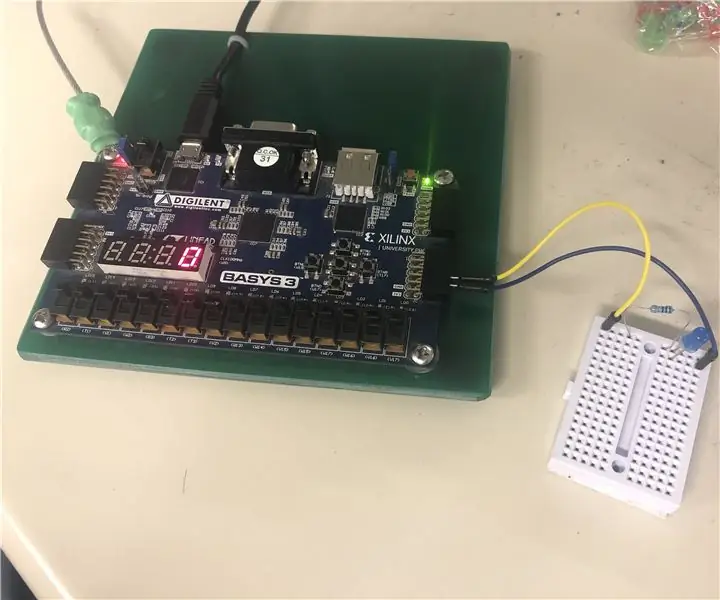

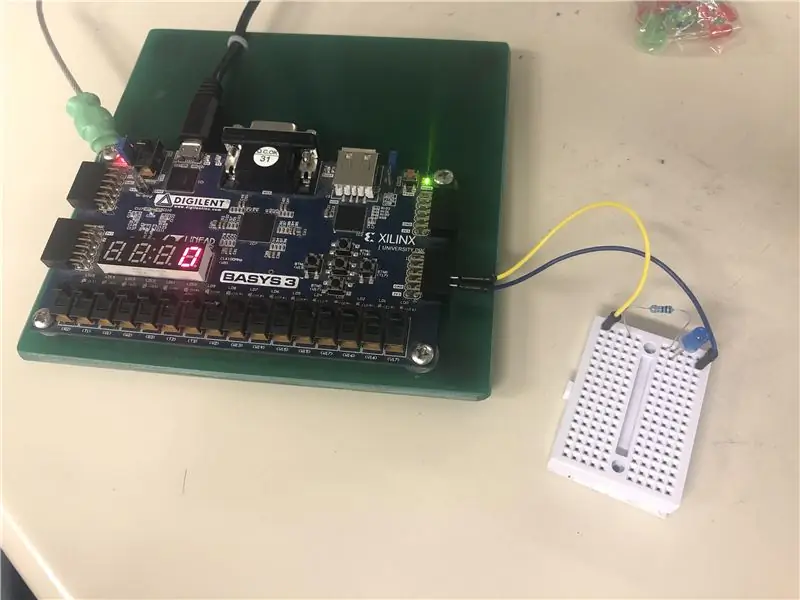

En aquesta guia anem a construir i controlar un sistema d’enfosquiment LED extern. Amb els botons disponibles, l'usuari pot atenuar la bombeta LED fins a la brillantor desitjada. El sistema utilitza la placa Basys 3 i està connectat a una placa de control que conté una resistència i la bombeta LED. En prémer el botó designat "amunt" augmentarà la brillantor i, en prémer el botó "avall", disminuirà la brillantor fins a zero. Això no només impedeix que l’usuari quedi cegat per les bombetes brillants com el sol, sinó que també conserva energia.

Pas 1: creeu un comptador d'entrada

Per a aquest pas, creem el component que determina el nivell de brillantor (mitjançant un rellotge) mitjançant dos commutadors: un per augmentar i un per disminuir. Mitjançant VHDL, vam produir el comptador mitjançant l’ús de xancletes D. En prémer el botó "amunt", el següent estat passa a l'estat actual, sortint a la pantalla de set segments i a la bombeta LED.

l'entitat updown_counter és

Port (present_state: out STD_LOGIC_VECTOR (3 downto 0); previous_state: in STD_LOGIC_VECTOR (3 downto 0); next_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; down_enable: in STD_LOGIC; acabar updown_counter; arquitectura El comportament de updown_counter és begin flop: process (next_state, clk, up_enable, down_enable, previous_state) begin if (rising_edge (clk)) then if (up_enable = '1' and not (next_state = "0000")) then present_state <= next_state; elsif (down_enable = '1' and not (previous_state = "1111")) then present_state <= previous_state; acabar si; acabar si; finalitzar el fracàs del procés; final Conductual;

També necessitem un rellotge per a cada entrada on es fixi (quan augmenti), de manera que també hem creat un divisor de rellotge que determina la rapidesa amb què es poden prémer els botons entre cada nivell de brillantor. Aquest divisor de rellotge ens permet mostrar correctament el nivell adequat a la pantalla de set segments i produir el nivell d’intensitat adequat per a cada nivell.

l'entitat counter_clkDiv és

Port (clk: in std_logic; sclk: out std_logic); end counter_clkDiv; l'arquitectura my_clk_div de counter_clkDiv és constant max_count: enter: = (10000000); senyal tmp_clk: std_logic: = '0'; begin my_div: process (clk, tmp_clk) variable div_cnt: enter: = 0; començar if (rising_edge (clk)) llavors if (div_cnt> = MAX_COUNT) llavors tmp_clk <= no tmp_clk; div_cnt: = 0; else div_cnt: = div_cnt + 1; acabar si; acabar si; sclk <= tmp_clk; finalitza el procés my_div; acabar my_clk_div;

Pas 2: Creeu un divisor de rellotge LED

Per a aquest pas, creem un divisor de rellotge per a la bombeta LED per determinar 16 nivells d'intensitat diferents. Amb 0 desactivat fins a 15 que mostra la brillantor màxima, el divisor de rellotge augmenta cada pulsació de botó pel que establim que serà el nivell de brillantor. Cada nivell creixent significava un augment del rellotge de la bombeta LED. Recordant que la brillantor no augmenta linealment, hem ajustat el rellotge fins al màxim i hem reduït els rellotges en conseqüència.

Nota: fem servir un LED blau. L’ús d’un color diferent (com el vermell) requerirà rellotges lleugerament diferents; un paràmetre de brillantor mitjà per al blau ja podria ser el màxim per al vermell. Això passa perquè diferents longituds d'ona de llum requeriran diferents quantitats d'energia, amb els colors més freds com el porpra i el blau que requereixen més energia, mentre que els colors més càlids com el vermell i el taronja requereixen menys energia.

l'entitat led_clkDiv és Port (present_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; led_clk: out STD_LOGIC); end led_clkDiv; arquitectura El comportament de led_clkDiv és el senyal tmp_clk: std_logic: = '0'; variable compartida max_count: enter; begin count_stuff: process (present_state) begin case present_state és quan "0000" => max_count: = 0; quan "0001" => max_count: = 2; quan "0010" => max_count: = 4; quan "0011" => max_count: = 6; quan "0100" => max_count: = 8; quan "0101" => max_count: = 10; quan "0110" => max_count: = 12; quan "0111" => max_count: = 14; quan "1000" => max_count: = 16; quan "1001" => max_count: = 25; quan "1010" => max_count: = 50; quan "1011" => max_count: = 100; quan "1100" => max_count: = 150; quan "1101" => nombre_màxim: = 200; quan "1110" => max_count: = 250; quan "1111" => max_count: = 300; cas final; finalitzar el procés count_stuff; my_div: process (clk, tmp_clk, present_state) variable div_cnt: enter: = 0; començar if (rising_edge (clk)) llavors if (div_cnt> = max_count) llavors tmp_clk <= no tmp_clk; div_cnt: = 0; else div_cnt: = div_cnt + 1; acabar si; acabar si; led_clk <= tmp_clk; finalitza el procés my_div; final Conductual;

Pas 3: creació del controlador LED

Ara que hem arribat fins aquí, és el moment de combinar finalment tots els components que hem creat fins ara al fitxer LED Controller.

En resum, els components utilitzats són els següents:

- Comptador d'entrada (updown_counter)

- Divisor de rellotge (counter_clkDiv)

- Divisor de rellotge LED (led_clkDiv)

- Controlador de pantalla de set segments (sseg_dec) (fitxer adjunt)

En realitat, no es va discutir prèviament el controlador de pantalla de set segments perquè en realitat vam agafar el fitxer VHDL al Dr. Bryan Mealy a causa del seu llarg i complicat codi. El que fa essencialment és conduir les entrades dels nostres botons a la pantalla de set segments de la placa Basys 3 per tal de saber quin nivell de brillantor està activat.

Per avançar, el controlador LED utilitza xancletes per augmentar o disminuir el recompte que controla simultàniament la pantalla de set segments i el nivell de brillantor de la bombeta LED.

el comptador d’entitats és Port (clk: in STD_LOGIC; up_enable: in STD_LOGIC; down_enable: in STD_LOGIC; SEGMENTS: out STD_LOGIC_VECTOR (7 downto 0); DISP_EN: out STD_LOGIC_VECTOR (3 downto 0); led_clk: out STD_LOG; comptador final; arquitectura El comportament del comptador és el component updown_counter és Port (present_state: out STD_LOGIC_VECTOR (3 downto 0); previous_state: in STD_LOGIC_VECTOR (3 downto 0); next_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; up_enable: a STD_LOGIC); component final updown_counter; component counter_clkDiv és Port (clk: in std_logic; sclk: out std_logic); component final counter_clkDiv; component sseg_dec és Port (ALU_VAL: en std_logic_vector (7 fins a 0); SIGN: en std_logic; VÀLID: en std_logic; CLK: en std_logic; DISP_EN: out std_logic_vector (3 fins a 0); SEGMENTS: out std_logic_vector) (7 downt); component final sseg_dec; component led_clkDiv és Port (present_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; led_clk: out STD_LOGIC); component final led_clkDiv; signal present_state: STD_LOGIC_VECTOR (3 downto 0): = "0000"; senyal next_state: STD_LOGIC_VECTOR (3 fins a 0): = "0000"; senyal anterior_estat: STD_LOGIC_VECTOR (3 fins a 0): = "0000"; senyal Alu_Val: STD_LOGIC_VECTOR (7 a 0); senyal sclk: STD_LOGIC; començar Alu_Val (7 fins a 4) <= "0000"; Alu_Val (3 fins a 0) <= present_state; next_state (0) <= not (present_state (0)); next_state (1) <= present_state (0) xor present_state (1); next_state (2) <= (present_state (0) and present_state (1)) xor present_state (2); next_state (3) <= (present_state (0) and present_state (1) and present_state (2)) xor present_state (3); previous_state (0) <= not (present_state (0)); previous_state (1) <= present_state (0) xnor present_state (1); previous_state (2) <= (present_state (0) ni present_state (1)) xor present_state (2); previous_state (3) sclk, next_state => next_state, previous_state => previous_state, up_enable => up_enable, down_enable => down_enable, present_state => present_state); visualització: mapa de ports sseg_dec (ALU_VAL => Alu_Val, SIGN => '0', VALID => '1', CLK => clk, DISP_EN => DISP_EN, SEGMENTS => SEGMENTS); led_div: led_clkDiv mapa de ports (clk => clk, present_state => present_state, led_clk => led_clk); clk_div: counter_clkDiv mapa de ports (clk => clk, sclk => sclk); final Conductual;

Pas 4: Establir restriccions i muntatge

Restriccions

Per configurar i programar correctament la placa Basys 3, primer hem de configurar el nostre fitxer de restriccions adjunt a aquest pas. S'han ajustat els paràmetres següents:

Botons

- S'ha canviat T18 a "up_enable" (augmenta la brillantor)

- S'ha canviat U17 a "down_enable" (disminueix la brillantor)

Pantalla de 7 segments

- W7, W6, U8, V8, U5, V5, U7, V7 representen cada segment d’una pantalla

- U2, U4, V4, W4 representen cada ànode que es mostra (només 2 estan actius perquè el nostre nombre més alt és 15)

Capçalera PMOD JC

JC7 és on connectem un dels cables de la bombeta LED i l’altre cable condueix a terra

Després de configurar-ho tot, tot el que heu de fer és generar el vostre flux de bits (amb qualsevol programari que utilitzeu, és a dir, Vivado), programar el tauler i boom. T’has aconseguit una taula de treball.

Nota: El mapatge de pins es pot trobar al full de dades de Basys 3 aquí.

muntatge

Pas 5: utilitzar el commutador de regulador

Si tot va bé, hauríeu de tenir un sistema dimmer totalment funcional. En resum, si premeu el botó superior augmentareu la brillantor (fins a 15) i, si premeu el botó avall, disminuïu la vostra brillantor (fins a 0). Espero que tot vagi bé per la vostra vista ara relaxada.

Recomanat:

Live Covid19 Tracker mitjançant ESP8266 i OLED - Tauler de control Covid19 en temps real: 4 passos

Live Covid19 Tracker mitjançant ESP8266 i OLED | Tauler de control Covid19 en temps real: visiteu el lloc web de Techtronic Harsh: http: //techtronicharsh.com. Es va fer necessari vigilar l’escenari actual de COVID-19 al món. Així doncs, estar a casa era aquest el

Tauler LED regulable: 15 passos (amb imatges)

Panell LED regulable: quan vaig veure el concurs de LED, em va fer pensar si hi havia alguna cosa que fos divertit fer que s'utilitzessin LEDs. Realment no sóc un home elèctric, així que vaig pensar que seria un repte divertit. Feia temps que buscava aconseguir una làmpada de treball, així que

Tauler lleuger o tauler de vidre: 4 passos

DIY Lightboard o Glassboard: Hi ha moltes innovacions en el sector educatiu. L’ensenyament i l’aprenentatge a través d’Internet ja són coses quotidianes. La majoria de les vegades els tutors en línia tendeixen a centrar-se més en el contingut tècnic, deixant als espectadors desinteressats. Aprenentatge en 3D

Domòtica: Tauler de commutació automàtic amb control de regulació mitjançant Bluetooth mitjançant Tiva TM4C123G: 7 passos

Domòtica: placa de commutació automàtica amb control dimmer mitjançant Bluetooth mitjançant Tiva TM4C123G: Avui en dia tenim comandaments a distància per als nostres aparells de televisió i altres sistemes electrònics, que ens han facilitat la vida. Alguna vegada us heu preguntat sobre la domòtica que donaria la possibilitat de controlar llums de tubs, ventiladors i altres elements elèctrics

Projecte de tauler de puntuació amb pantalla LED P10 mitjançant DMD: 6 passos (amb imatges)

Projecte de tauler de puntuació amb pantalla LED P10 mitjançant DMD: sovint ens trobem en un estadi de futbol; hi ha un tauler LED gegant que serveix de marcador. Així també en altres camps esportius, també sovint coneixem el marcador de la pantalla de LED. Tot i que no és possible, també hi ha un camp que encara ens segueix